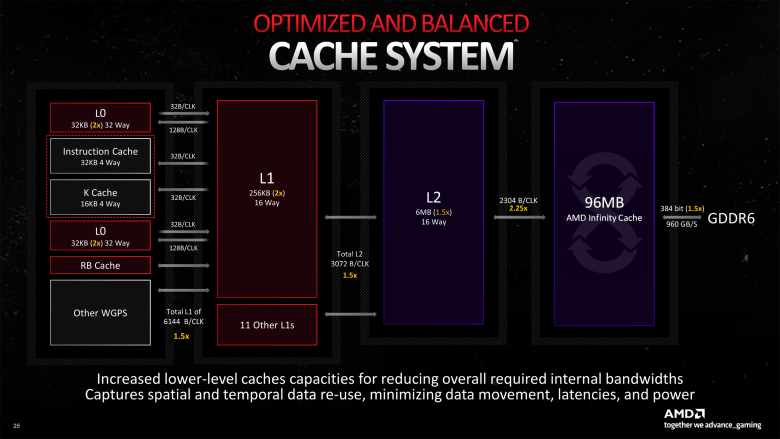

AMD zrychlila cache RDNA 3 o více než 60 % na všech úrovních

V nových materiálech k architektuře RDNA 3 a GPU Navi 21 zpřístupnila AMD další údaje ke struktuře a charakteristice cache od úrovně L0 až po Infinity Cache.

Tabulku, kterou jsme vám nabídli krátce po ohlášení architektury, si můžeme upřesnit a výrazně rozšířit:

| Navi 31 Radeon RX 7900 | Navi 21 Radeon RX 69x0 XT | |

|---|---|---|

| L0$ | 3 MB (+240 % +140 % / 2,4×) | 1,25 MB |

| L1$ | 3 MB (+300 % +200 % / 3×) 6144 b/takt (+50 % / 1,5× na takt) 14,67 TB/s (+63 % / 1,63×) | 1 MB 4096 b/takt 9,02 TB/s |

| L2$ | 6 MB (+50 % / 1,5×) 3072 b/takt (+50 % / 1,5× na takt) 7,34 TB/s (+63 % / 1,63×) | 4 MB 2048 b/takt 4,51 TB/s |

| ∞$ | 96 MB (-25 % / 0,75×) 2304 b/takt (+125 % / 2,25× na takt) 4,34-5,3 TB/s (+117-165 % / 2,17-2,65×) | 128 MB 1024 b/takt 2,0 TB/s |

Datová propustnost od L1 cache k L0 cache dosahuje téměř 15 TB/s, tedy skoro o dvě třetiny více než u Navi 21. Od L2 cache k L2 cache proudí data rychlostí 7,34 TB/s, což je rovněž navýšení přesahující šedesát procent. Mezi L2 cache a Infinity Cache je dosahováno přenosové rychlosti 5,3 TB/s; podle všeho to však může zahrnovat i data proudící z VRAM, takže v závislosti na tom, zda jsou přesouvána pouze data z Infinity Cache nebo zároveň využívána i data z VRAM, může být propustnost 4,34-5,3 TB/s, tedy 2,17-2,65× navýšena mezigeneračně.

Datová propustnost L0, L1 a L2 cache závisí na taktech 5nm čipletu, takže u výše taktovaných produktů (než Radeonu RX 7900 XTX) může být úměrně taktům vyšší.

AMD