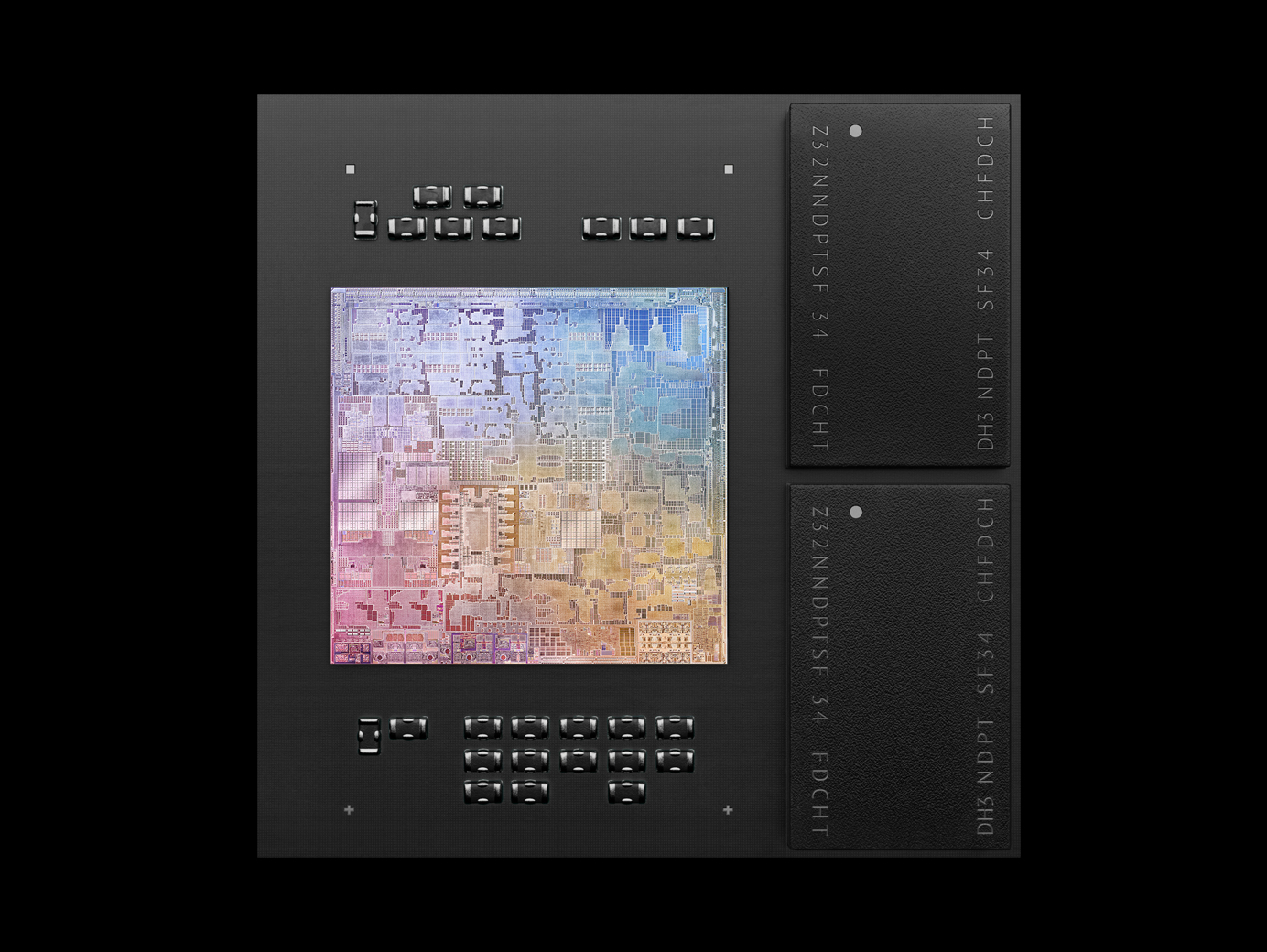

Apple prý lhal o výrobě A16 na 4nm procesu, zatímco interně jej značil jako 5nm

Tato (řekněme) informace pochází od uživatele Unknownz21, který měl možnost vidět nějaké materiály Applu a na jejich základě zveřejnil několik příspěvků o SoC A16 a A17, přičemž klíčová je věta…

An interesting tidbit about the A16 - looks like the whole “4nm” thing was apparently a marketing gimmick, I’ve seen it labeled as a 5nm chip internally. --- Unknownz21 |

…ve které tvrdí, že celá „4nm“ věc byla zjevně jen marketingový trik, protože viděl interní materiály, kde byl čip označen jako 5nm.

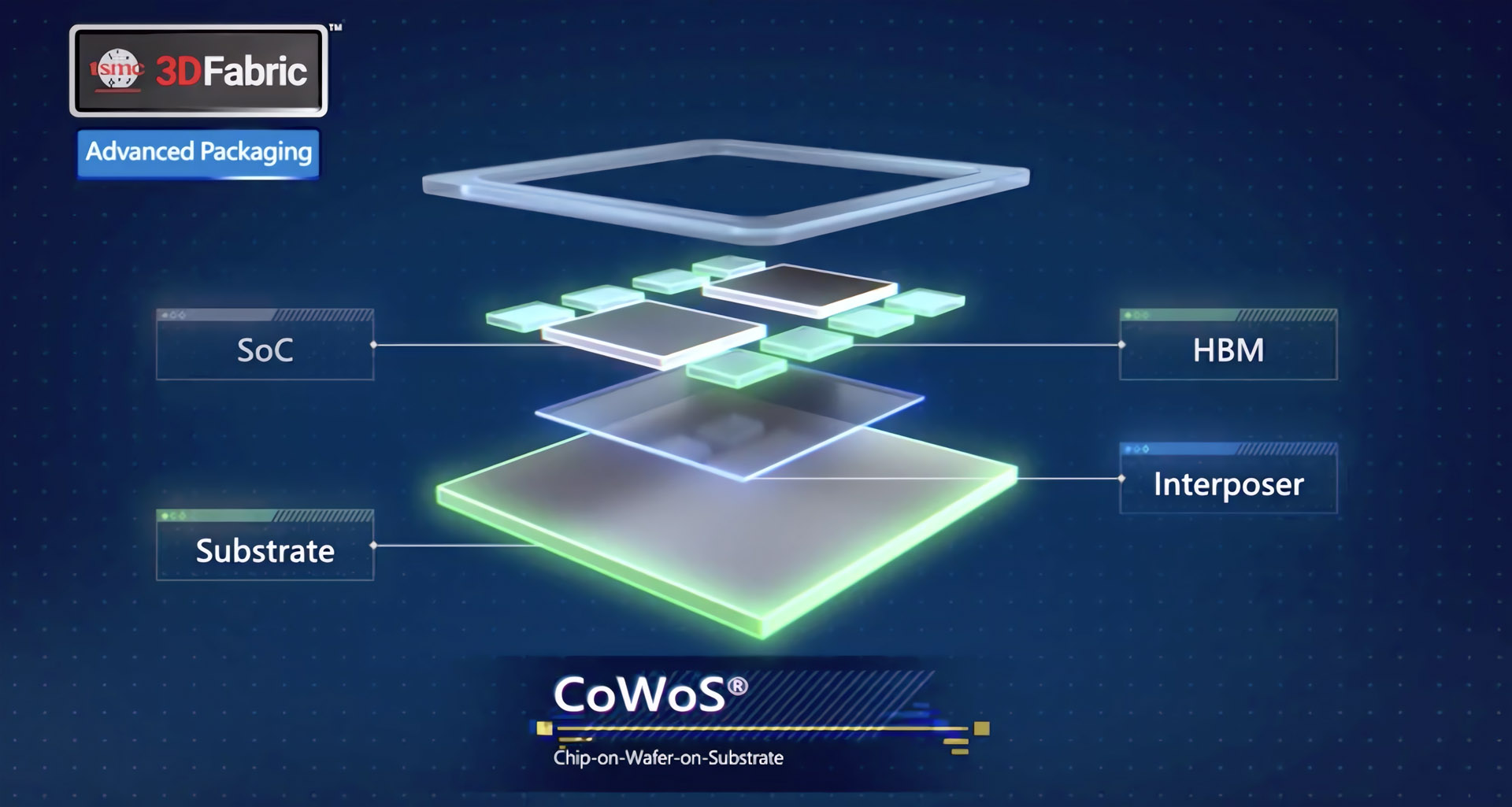

Problém celého sdělení spočívá v tom, že čip klidně může být interně značen jako 5nm a přitom být 4nm. Důvod je prostý. 4nm proces TSMC (N4) je totiž derivátem 5nm procesu TSMC (N5). Tím se ani TSMC netají, naopak od jeho uvedení to aktivně prezentuje:

In addition, TSMC plans to launch 4nm (N4) technology, an enhanced version of N5 technology. N4 provides further enhancement in performance, power and density for the next wave of N5 products. The development of N4 technology is on schedule with good progress, and volume production is expected to start in 2022. --- TSMC |

Informace o 4nm procesu pověsila na svůj web TSMC již v roce 2021 a již tehdy uváděly, že „TSMC plánuje vydat 4nm (N4) technologii, vylepšenou variantu N5 technologie“. Aby nebyly pochybnosti, ocituji ještě slova jednoho z šéfů TSMC, který k příležitosti odhalení plánů společnosti na jaře 2021 zmínil jeden podstatný detail:

N4 is a straightforward migration from N5 with compatible design rules while providing further performance, power and density enhancement for the next wave of 5-nanometer products. N4 risk production is targeted for second half this year and volume production in 2022. --- C. C. Wei, TSMC |

Pan Wei zde říká, že „N4 je přímým krokem z N5 se zachováním kompatibility pro pravidla návrhu čipu“. Jinými slovy, že stačí mít jeden návrh čipu připravený podle jedněch pravidel a tento čip pak můžete vyrábět u TSMC jak na 5nm tak na 4nm procesu, aniž byste museli zasahovat do návrhu. Jde o obdobu toho, čemu TSMC dříve říkala „optical shrink“, tedy optické zmenšení návrhu (který pro toto zmenšení rovněž nebylo potřeba upravovat), případně lze situaci 5nm / 4nm procesu srovnávat se situacemi jaké někteří výrobci u některých procesů odlišovali přidáním znaménka „+“.

Jednoduše a krátce: Apple si zcela oprávněně mohl v interních dokumentech označit čip A16 jako 5nm a poté ho vyrábět na 4nm procesu, protože tak to prostě u této dvojice procesů funguje. 5nm návrh lze vyrábět na 5nm i 4nm linkách, protože jsou kompatibilní. Stejně jako si například AMD původně značila Zen+ jako 14nm nebo 14nm+ a reálně vznikl na 12nm procesu, když se GlobalFoundries vylepšené variantě původního 14nm procesu rozhodla říkat 12nm namísto 14nm nebo 14nm+. Senzace se tedy nekoná a celá situace je spíše kachnou vzniklou na základě přístupu k informaci, které leaker nerozuměl.