Intel chce PCI Express ×2 a rozhodně to není špatný nápad

Architektura PCI Express je poměrně hodně modulární. Na rozdíl od předchozí PCI, která byla z pohledu architektury klasickou sběrnicí, PCI Express je point-to-point s tím, že ji lze různě konfigurovat. PCI Express linky (anglicky „lane“, ale překlady jako „cesta“ a jemu podobné nám nikdy přes pysky ani přes prsty pořádně nešly) lze sdružovat a výsledné „porty“ jich mohou obsahovat více, konkrétně je možné utvořit PCI Express ×4, ×8 a ×16 porty, zejména proto, že pro takto zkonfigurované porty existují fyzické sloty (samozřejmě včetně PCI Express ×1). Pro PCI Express ×2 žádný slot neexistuje.

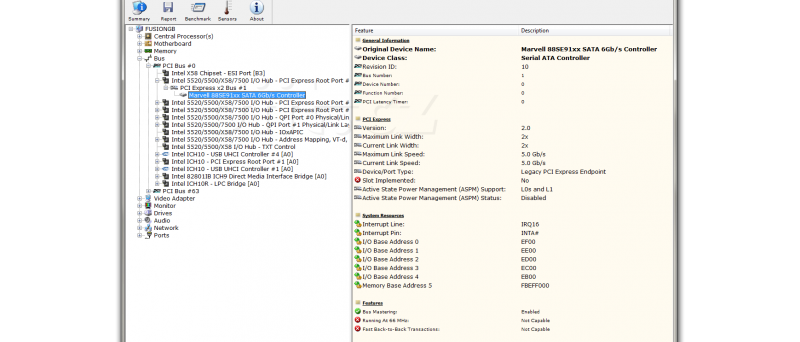

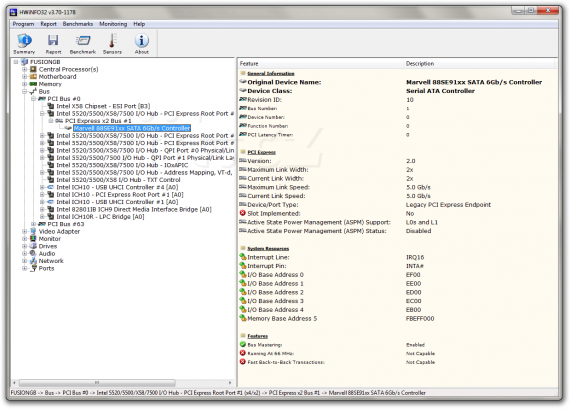

Přesto už jsme se s PCI Express ×2 v praxi setkali, a to konkrétně na hustodémonsky krutopřísné desce Gigabyte G1.Assassin. Ta obsahuje kromě jiného SATA řadič Marvell 88SE9182, což je shodou okolností čip připojitelný právě přes dvě PCI Express linky a tak je i zapojen na této desce, a to přímo do jejího severního můstku Intel X58.

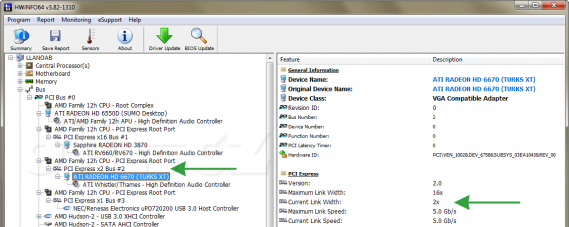

Sluší se zmínit, že máme momentálně v redakci tu čest s jednou deskou, která umí taky udělat PCI Express ×2, a to dokonce ve formě slotu. Je to ASUS F1A75-V PRO a za určitých okolností dostává druhý PCI Express ×16 slot pouze dvě linky (zde vložená grafika pak skutečně běží v režimu PCI Express ×2).

Důvod, proč to není PCI Express ×4, možná pochopíte z obrázku sami, pokud ne, počkejte si na recenzi, tam to bude podrobně vysvětleno.

Každopádně mezi PCI Express ×1 a PCI Express ×4 opravdu je velká mezera, kterou by Intel rád vyplnil. Ono to má i další důvod. Vezměte si, že v procesoru má Intel 16 PCI Express linek, v čipsetu pak dokonce jen 8. V procesoru to můžete dělit na ×8/×8 a tím jste skončili, takže když první polovinu z těchto 16 linek pošlete např. do nForce 200 čipu, abyste dostali dostatek ×16 slotů pro grafiky, druhou polovinu buďto využijete na nějaký nadupaný ×8 řadič (většinou tomu tak není), nebo z ní využijete jen 4 linky na méně nadupaný řadič (a ani to jsme ještě neviděli), anebo (nejčastěji) sem výrobce prskne USB 3.0 řadič s jednou jedinou mrzkou linkou, nazve to marketingově „USB 3.0 Turbo“ a 7 linek doslova „vyhodí do kanálu“.

Řešení by bylo v přijetí PCI Express ×2, možnosti dělit PCI Express linky procesoru do většího množství portů (než jen dvou) a vyrábění řadičů (ať už USB 3.0, nebo SATA/RAID) s PCI Express ×2 konektivitou. Tím se PCI Express linky rozmělní do většího počtu a mohou tak být efektivněji využity. V AMD už to nejspíše pochopili po svém, procesor „Llano“ má PCI Express linek rovnou 20 a zbylé čtyři (po využití prvních šestnácti na PCI Express ×16 slot) umí dělit i po dvou na zatím neoficiální PCI Express ×2. Intel to samozřejmě na některých svých produktech umí taky, takže „živná půda“ pro příchod PCI Express ×2 je každopádně připravena. Věříme, že vytvoření fyzického PCI Express ×2 slotu bude tím nejmenším problémem. Co bude potřeba udělat především, je nejspíše přesvědčit PCI-SIG, aby oficiálně posvětila existenci PCI Express ×2.

Pro názornost jsme se pokusili „vyrobit“ takový PCI Express ×2 slot a protože je hodně podobný PCI Express ×1 slotu, udělali jsme obrázek animovaný. Vycházíme z toho, že každá PCI Express linka navíc si vezme 4 dvojice pinů (po obou stranách). Popis pinů je třeba zde na Wikipedii.

Animovaný náčrt srovnání „PCI Express ×2“ a PCI Express ×1 slotu