Intel představil Alder Lake: +19 % IPC a hardwarový scheduler Thread Director

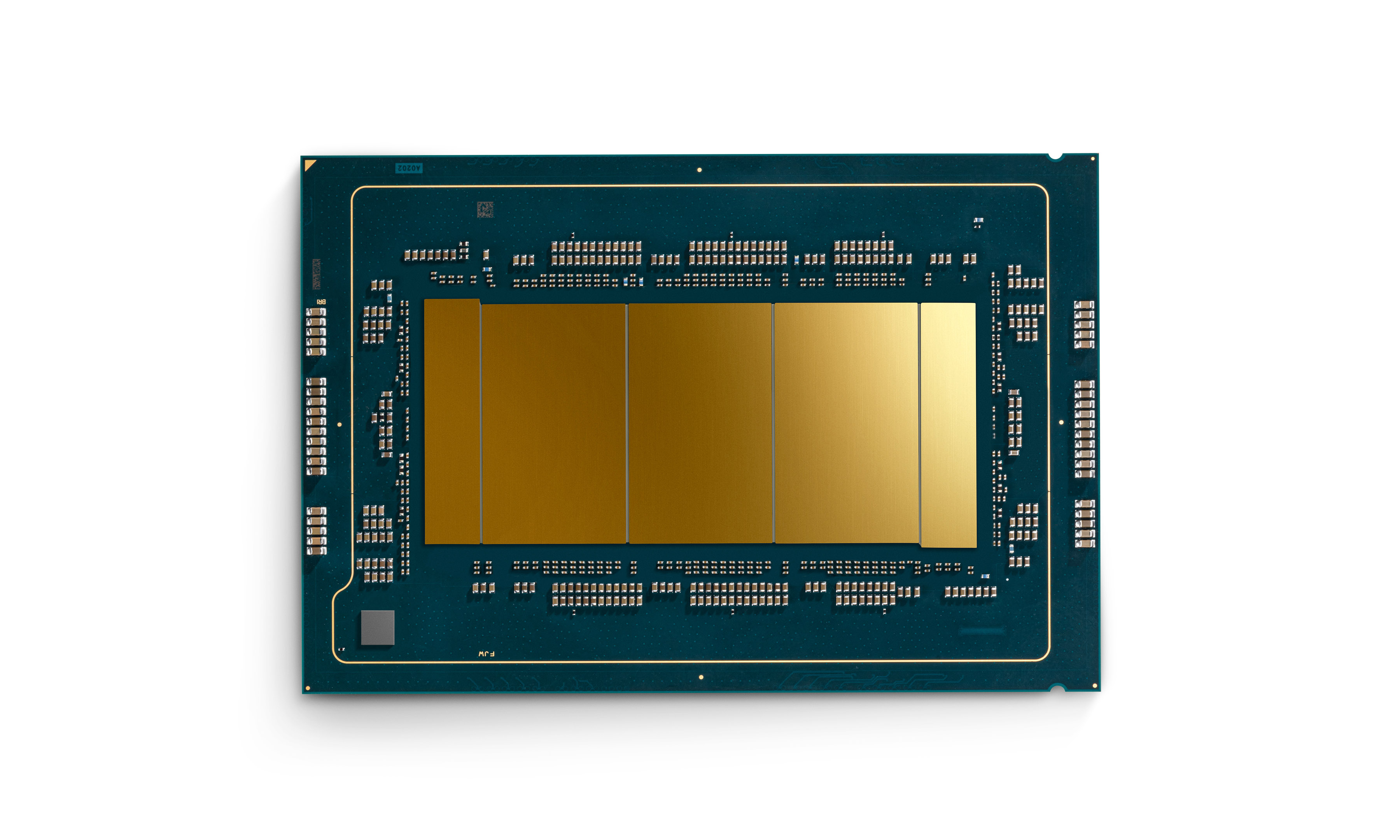

Řada Alder Lake bude stát na třech konfiguracích křemíku:

Pro desktop (socket LGA) půjde o křemík s fyzicky 8 velkými a 8 malými jádry. Mobilní segment dostane křemík s 6 velkými a 8 malými jádry a ultramobilní zařízení (15W notebooky a úspornější zařízení) dostanou křemík se 2 velkými a 8 malými jádry. Další segmentace už bude řešena počtem (ne)aktivních jader.

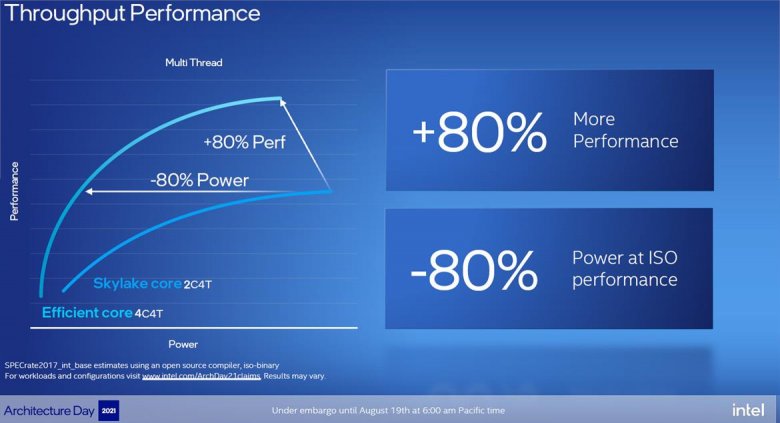

Jednou ze zásadních novinek Alder Lake je přítomnost malých jader. Jejich výhodu lze využít v mobilním segmentu, kde mohou fungovat jako prvek snižující spotřebu v nenáročných úlohách a desktopovém segmentu, kde mohou fungovat jako prvek zvyšující vícejádrový výkon ve vícevláknových úlohách. Doposud se o malých jádrech architektury Gracemont proslýchalo, že by mohla dosahovat 60 % IPC Skylake a v situacích výhodných pro tuto architekturu až 80 % IPC Skylake. Intel se je však rozhodl prezentovat nikoli z hlediska IPC, ale z hlediska energetické efektivity. Uvádí, že čtyři jádra Gracemont dosahují při stejné spotřebě se dvěma jádry Skylake o 80 % vyššího výkonu. Při nastavení, ve kterém dosahují stejného výkonu, pak dosahují o 80 % (5×!) nižší spotřeby.

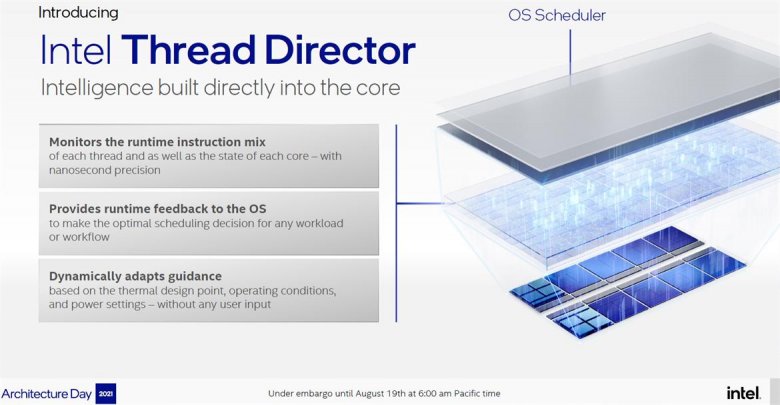

Aby zátěž byla delegována na správná jádra (a výpočetně náročné úlohy nekončily na malých jádrech a naopak úlohy běžící na pozadí neaktivovaly velká jádra), implementoval Intel do Alder Lake hardwarový scheduler, jak se předpokládalo. Ten nese označení Thread Director a vyhodnocuje instrukce použité jednotlivými vlákny a na základě toho instruuje scheduler operačního systému.

Datové rozhraní mezi procesorovými jádry je schopno přenášet až 1000 GB/s, rozhraní k paměťovému systému až 204 GB/s a rozhraní pro IO až 64 GB/s. 64 GB/s odpovídá požadavkům PCIe 5.0 rozhraní (k tomu se ještě dostaneme), ale údaj 204 GB/s pro paměťový subsystém nedává dobrý smysl. Alder Lake disponuje dvěma kanály s podporou DDR5 pamětí, které při počátečních 4800 Gb/s dosahují 76,8 GB/s a při cílových (maximum specifikace JEDEC) 6400 Gb/s pak 102,4 GB/s. Jak lze v praxi dosáhnout prakticky dvojnásobné hodnoty, Intel neuvádí.

Ačkoli je Alder Lake Intelem od počátku proklamován jako PCIe 5.0 řešení, bude nakonec vybaven verzí 5.0 pouze pro šestnáct linek (slot grafické karty). Ostatní rozhraní jsou verze 4.0 (čtyři linky na procesoru) a generacemi 4.0 a 3.0 na úrovni čipsetu. Debaty na téma PCIe 5.0 SSD tak zpětně ztrácejí význam.

Podobný háček se týká (např. výše znázorněným slajdem) proklamovaná podpora Thunderbolt 4. Ta se ve skutečnosti týká jen mobilní verze. Desktopová (která je na slajdu zobrazena) rozhraní Thunderbolt 4 nenabízí a pokud by jím měla být základní deska vybavena, bylo by nutné osadit samostatný řadič.

Třetí detail se týká IPC. Intel byl tentokrát konkrétnější a výslovně uvedl, že 19% nárůst IPC není vyčíslen oproti nejpokročilejší dosavadní architektuře Intelu Willow Cove / Tiger Lake, ale oproti o generaci starší Cypress Cove / Rocket Lake (tzn. desktopová verze Sunny Cove / Ice Lake). To samozřejmě nic nemění na faktu, že IPC velkých jader Alder Lake bude podstatně vyšší než IPC Zen 3, ale znamená to, že nebude vyšší o očekávaných ~20 %, ale spíš tak o 12-15 %. Dále to znamená, že dosavadní úniky výkonnostních testů pocházejí z případů zobrazených v pravé polovině grafu. Druhá věc je, že Alder Lake nestojí jen na IPC, ale také na vysokých taktech, které jsou o >8 % nad současným top modelem architektury Zen 3, takže IPC v kombinaci s takty 21-24 % náskok jednojádrového výkonu nad Zen 3 vytáhne (nepůjde však o 29-30 % nad Zen 3).

Desktopový Alder Lake tak celkem nabídne až 16 procesorových jader (až 8 velkých, až 8 malých), což znamená až 24 vláken (16 na velkých jádrech, 8 na malých) a až 30 MB cache poslední úrovně.