Intel uvádí procesory Core2 Duo a Core2 Extreme a čipsety

Kapitoly článků

Mikroarchitektura Intel Core

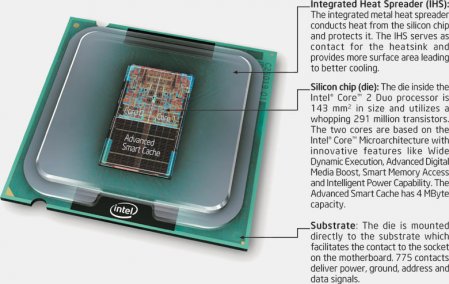

Na začátek si povězme něco málo o procesoru s kódovým jménem „Conroe“, který je dnes uváděn coby Core2 Duo a Core2 Extreme. Ještě před tím vším je nutné dodat, že ne všechny procesory Core2 Duo jsou skutečně „Conroe“. Některé z nich by totiž měly nést kódové jméno „Allendale“. Ten se od Conroa liší polovinou L2 cache, Allendale má tedy celkem 2 MB. Jádro Conroe vyráběné 65nm procesem sestává z celkem asi 291 miliónů tranzistorů na ploše 143 mm² (pro srovnání 90nm Smithfield coby první dvoujádrový procesor zabíral při 230 miliónech tranzistorů 206 mm² a třeba Athlon 64 FX-62 pro socket AM2 zabírá při 90nm výrobním procesu se svými 227 milióny tranzistorů plochu 230 mm²).

Na začátek si povězme něco málo o procesoru s kódovým jménem „Conroe“, který je dnes uváděn coby Core2 Duo a Core2 Extreme. Ještě před tím vším je nutné dodat, že ne všechny procesory Core2 Duo jsou skutečně „Conroe“. Některé z nich by totiž měly nést kódové jméno „Allendale“. Ten se od Conroa liší polovinou L2 cache, Allendale má tedy celkem 2 MB. Jádro Conroe vyráběné 65nm procesem sestává z celkem asi 291 miliónů tranzistorů na ploše 143 mm² (pro srovnání 90nm Smithfield coby první dvoujádrový procesor zabíral při 230 miliónech tranzistorů 206 mm² a třeba Athlon 64 FX-62 pro socket AM2 zabírá při 90nm výrobním procesu se svými 227 milióny tranzistorů plochu 230 mm²).

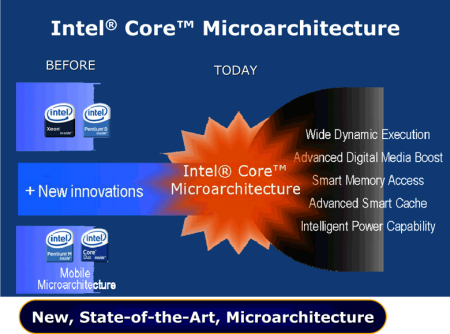

Ačkoli je Core2 Duo svým značením nástupcem Core Duo a tak trochu z něj i vychází (ono Core Duo vlastně vychází z Pentia M neboli mikroarchitektury, které Intel říká „Banias“, což je také kódové jméno prvního skutečně mobilního procesoru Intelu), vylepšení je poměrně hodně a tak dostala tato mikroarchitektura nové jméno Intel Core. O té si dnes povíme něco málo navíc oproti stručnému výtahu z loňského podzimního IDF.

Macro-Fusion

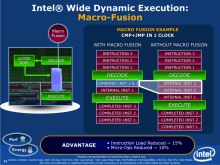

Pod pojmem Intel Wide Dynamic Execution se ukrývá několik věcí, nejzajímavější je asi Macro-Fusion, což můžeme jednoduše vysvětlit jako slučování několika instrukcí do jediné. Jako typický příklad používá Intel ve svých prezentacích ukázku na instrukcích CMP a JNE (jedna z nich stručně řečeno cosi porovná a druhá na základě výsledku tohoto srovnání buď skočí na jinou část programu nebo se pokračuje normálně dál). Tyto dvě instrukce dokáže procesor sloučit do jedné CMPJNE, kterou pak vykoná během jediného hodinového cyklu.

Macro-Fusion samozřejmě není jedinou urychlující záležitostí, která spadá pod Intel Wide Dynamic Execution. Z dalších ještě zmiňme poněkud větší out-of-order úložiště (instrukce se v procesorech již nějaký ten čas zpracovávají v řekněme „vhodnějším“ pořadí než v jakém to nařizuje program) či schopnost zpracovat až čtyři mikroinstrukce za takt (mikroinstrukce jsou vlastně jakési instrukce procesoru takřka nejbližší, které si procesor vytváří z příchozích x86 instrukcí – dosavadní procesory uměly maximálně tři mikroinstrukce za takt).

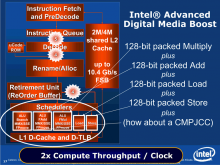

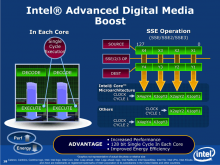

Advanced Digital Media Boost

Tato technologie zjednodušeně řečeno urychluje výpočty, kde se používají SSE instrukční sady (SSE až SSE3 a nově i SSE4, což je však spíše zjednodušeně řečeno „novější revize SSE3“ než nějaké skutečné označení, ani Intel o tom jako o SSE4 nehovoří, ale některé programy, třeba CPU-Z, SSE4 ve vlastnostech procesoru zmiňují). Jednotky pro SSE operace, které přicházejí ke slovu hlavně v multimediálních aplikacích, jsou 128bitové a instrukce se zpracovávají v jediném hodinovém taktu. Zde nastává zajímavé zrychlení hlavně ve hrách, které s SSE instrukcemi dost pracují.

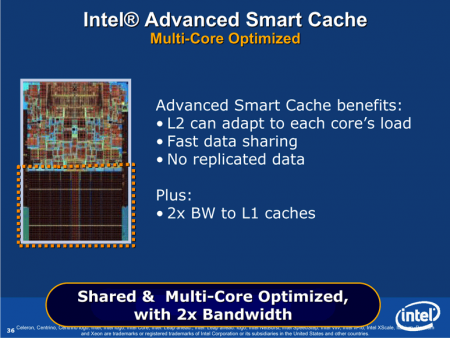

Smart Memory Access, Smart Cache

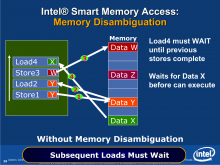

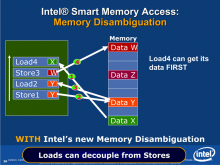

Smart Memory Access zvyšuje výkon systému optimalizací využití datového toku z procesoru do paměti, čímž mimo jiné kompenzuje i nemalé latence při přístupu do paměti. K tomu procesoru pomáhá nová vlastnost s názvem „Memory disambiguation“, která se snaží zvýšit efektivitu out-of-order zpracování instrukcí lepším odhadováním pořadí zpracovávaných instrukcí.

Se Smart Memory Access ještě tak trochu souvisí i Smart Cache neboli sdílená L2 cahce mezi oběma jádry procesoru. Tuto vlastnost měl již procesor Core Duo, Core2 Duo k ní navíc ještě přidává schopnost, kdy obě jádra si mohou vyměňovat data „zkratkou“ rovnou z L1 cache jednoho do L1 cache druhého jádra a nemusejí tak zatěžovat L2 cache.

Intelligent Power Capability

Conroe (a samozřejmě i Allendale a mobilní Merom) mají mnohá vylepšení, která dovedou v procesoru povypínat docela velké množství nevyužívaných součástí. K nízké spotřebě přispívá i samotný 65nm výrobní proces a svým způsobem i fakt, že Core2 Duo neběhá na tak vysokých frekvencích, jako „netburstová“ Pentia D a Pentia 4. Procesory jsou vybaveny digitálními snímači teploty, mobilní Merom navíc i Power Status indikátory, které sdělují další informace o spotřebě zbytku systému. V neposlední řadě je i lépe využívána sběrnice (je jakoby rozdělena na části podle skutečného využití datového toku).