TSMC ohlásila A16, N4C, odklad backside power delivery a urychlení NanoFlex

Začněme s technologickými prvky procesů. Připomeňme, že 3nm proces ve variantě N3E přinesl technologii nazvanou FinFlex. Ta umožňuje v rámci jednoho čipu použít pro různé bloky (např. CPU část, GPU část a řadiče) použít odlišné konfigurace procesu, takže třeba pro CPU jádra může být použita verze optimalizovaná pro maximální frekvence (N3E 3-2 Fin), pro řadiče verze optimalizovaná na maximální denzitu (N3E 2-1 Fin) a pro GPU vyvážená mezi takty a denzitu (N3E 2-2 Fin).

NanoFlex

Od 2nm procesu používá TSMC tzv. GAA (NanoSheet) tranzistory, což poměrně zásadně změnilo strukturu procesu a umožnilo mixovat různé varianty procesu nejen na úrovni čipu, ale i na úrovni menších částí čipů, tzv. buněk. Lze si tak například představit, že cache procesoru a ALU procesoru budou postavené na dvou různých variantách procesu, které jsou pro dané využití optimální.

NanoFlex bude podporována u obou zatím ohlášených 2nm procesů TSMC a patrně i u jejich nástupců. S výrobou na 2nm procesu (N2) si mohou zákazníci TSMC pohrát od konce letošního roku, velkokapacitní výroba by se měla rozběhnout před pololetím roku příštího. V roce 2025 si ji tedy nejspíš vyzkouší Apple, do x86 světa se nedostane dříve než o rok později.

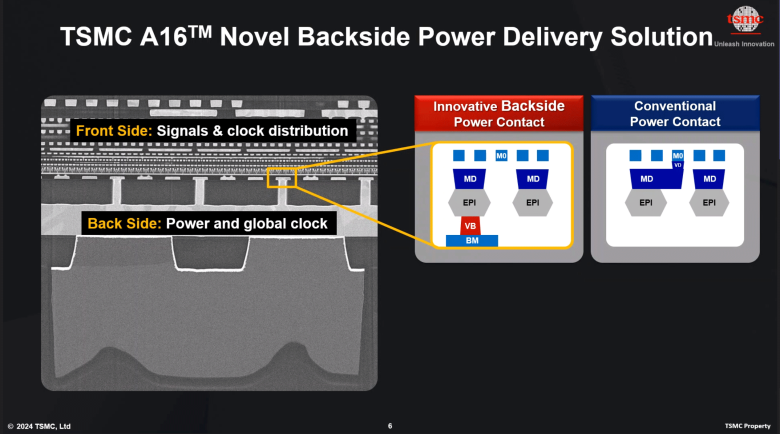

Backside Power Delivery

Technologie přesunu napájení na zadní stranu návrhu, která má zefektivnit napájení (zejména energetickou efektivitu) a také o něco snížit plochu, byla odložena.

Nedorazí s procesem N2P (druhá generace 2nm výroby chystaná na druhé pololetí 2025), ale s novým procesem A16, který dorazí více než o rok později.

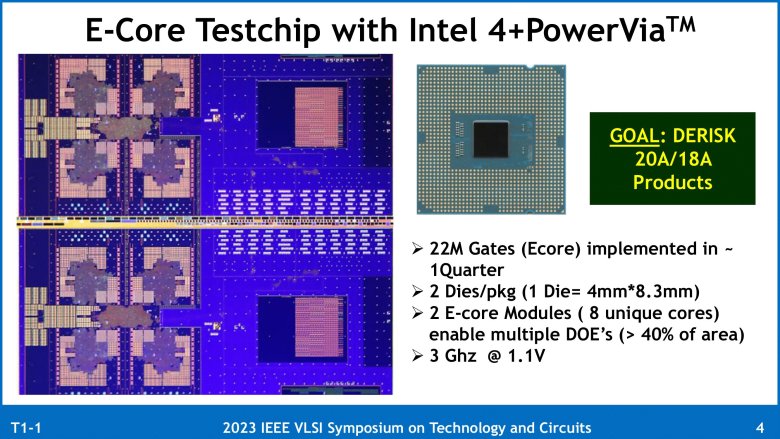

Loňské plány Intelu s PowerVia / Backside Power Delivery (Intel)

Připomeňme, že o Backside Power Delivery (v názvosloví Intelu PowerVia) mluvil Intel již se 4nm procesem, ale ten nakonec využil jen jako testovací platformu a komerčně bude technologie k dispozici na procesech Intel 20A a Intel 18A, v obou případech více či méně zpožděných.

| výrobce | proces | EUV | zahájení výroby / tape-out | velkokapacitní výroba |

|---|---|---|---|---|

| Samsung | 7nm LPE (1. gen.) | ? | nezahájena | |

| 7nm LPP (2. gen) | říjen 2018 | červen 2019 | ||

| 7nm (3. gen) | ? | ? | ||

| 6nm LPP | duben 2019 | H2 2019 | ||

| 5nm LPE | 4. 2019 / H2 2019 | H1 2020 | ||

| 5nm LPP | 2019? | 2021 | ||

| 4nm LPE (původní) | ? | 2020/21 zrušen | ||

| 4nm LPP (původní) | ? | 2022 zrušen | ||

| 4nm LPE (SF4E) | 2021? | 2022 | ||

| 4nm LPP (SF4) | ? | ? | ||

| 4nm LPP+ (SF4P) | ? | ? | ||

| 4nm HPC (SF4X) | ? | ? | ||

| 4nm LPA (SF4A) | ? | ? | ||

| 3nm (3GAE / SF3E) | Q4 2021 | H2 2022 jen interně | ||

| 3nm (3GAP / SF3) | ? | 2023 | ||

| 2nm (SF2) | ? | 2025 | ||

| 2nm (SF2P) | ? | 2026 | ||

| 1,4 nm (SF1.4) | ? | 2026 | ||

| TSMC | 7nm (N7) |  | leden 2017 | duben 2018 |

| 7nm (N7P) | ? | ? | ||

| 7nm EUV (N7+) | říjen 2018 | červen 2019 | ||

| 6nm | Q1 2020 | ? | ||

| 5nm (N5) | duben 2019 | H1 2020 | ||

| 5nm (N5P) | ? | 2021 | ||

| 4nm (N4) | Q3 2021 | Q1 2022 | ||

| 4nm (N4P) | H2 2022 | H2 2022 | ||

| 4nm (N4X) | H1 2023 | 2024 | ||

| 4nm (N4AE) | ? | 2024 | ||

| 4nm (N4C) | ? | 2025 | ||

| 3nm (N3/N3B) | Q4 2021 | prosinec 2022 | ||

| 3nm (N3E) | ? | Q3 2023→Q2 2023 | ||

| 3nm (N3P) | ? | 2024 | ||

| 3nm (N3S) | ? | 2024 | ||

| 3nm (N3X) | ? | 2025 | ||

| 3nm (N3AE) | ? | 2024 | ||

| 3nm (N3A) | ? | 2026 | ||

| 2nm (N2) | Q4 2024 | Q2 2025 | ||

| 2nm (N2P) | ? | H2 2025 | ||

| 1,6nm (A16) | ? | Q1 2027 |

TSMC N4C

Úplnou novinkou je 4nm proces N4C, který TSMC prezentuje jako řešení pro snížení výrobních nákladů, které vychází z procesu N4P. TSMC hovoří o 8,5% zlevnění výroby, kterého má být docíleno kombinací vyšší denzity a některých dílčích úprav výrobního procesu. Vyšší denzita patrně pochází hlavně z optimalizací pro SRAM. Teoreticky denzita stoupla maximálně o 8 %, reálně spíš méně (a zbytek poklesu nákladů pramení z jiných úprav).

Nástroje a návrhy jsou kompatibilní s procesem N4P, defektivita má být totožná, ale díky snížení plochy (více čipů na wafer) stoupne výtěžnost. Specifikace co do taktů a spotřeby TSMC neuvádí, takže lze očekávat stejnou úroveň jako u N4P nebo kosmetické zlepšení.

Proces má být ve fázi velkoobjemové výroby v příštím roce a jeho neplánované zařazení do nabídky může souviset s rostoucím zájmem o procesy Samsungu v souvislosti s levnějšími produkty.

| Samsung | |||

| proces | denzita | výkon | spotřeba |

|---|---|---|---|

| 7nm LPP (2. gen) | - | ? | ? |

| 7nm (3. gen) | +17% vs. 7LPP | ? | ? |

| 6nm LPP | +10 % vs. 7LPP | ? | ? |

| 5nm LPE | +25 % vs. 7LPP +33 % vs. 7LPP | +10 % vs. 7LPP | -20 % vs. 7LPP |

| 5nm LPP | ? | +5 % vs. 5LPE | -10 % vs. 5LPE |

| 4nm zrušen | „full node“ | ? | ? |

| 4nm LPE (SF4E) | +6 % vs. 5nm? | +8 % vs. 5LPE | -12 % vs. 5LPE |

| 4nm LPP (SF4) | ? | +5 % vs. 4LPE | -10 % vs. 4LPE |

| 4nm LPP+ (SF4P) | ? | ? | ? |

| 4nm HPC (SF4X) | ? | ? | ? |

| 4nm LPA (SF4A) | ? | ? | ? |

| 3nm (3GAE) | +45 % vs. 7LPP +33 % vs. 7LPP +35 % vs. 5LPE +20 % vs. 5nm | +30 % vs. 7LPP +10 % vs. 7LPP +35 % vs. 5LPE | -50 % vs. 7LPP -20 % vs. 7LPP -50 % vs. 5LPE |

| 3nm (SF3 / 3GAP) | +27 % vs. 4LPP +52 % vs. 5nm | +22 % vs. 4LPP | -34 % vs. 4LPP |

| 2nm (SF2) | +5 % vs. 3GAP | +12 % vs. 3GAP | -20 % vs. 3GAP |

| 2nm (SF2P) | ? | ? | ? |

| 1,4 nm (SF1.4) | ? | ? | ? |

| TSMC | |||

| proces | denzita | výkon | spotřeba |

| 7nm (N7) | +59 % vs. N10 | +35-40 % vs. N10 | -40 % vs. N10 |

| 7nm (N7P) | ? | +7 % vs. N7 | -10 % vs. N7 |

| 7nm+ (EUV / N7+) | +20 % vs. N7 | +10 % vs. N7 | -15 % vs. N7 |

| 6nm (N6) | +18 % vs. N7 | ? | ? |

| 5nm (N5) | +80 % vs. N7 | +15 % vs. N7 | -30 % vs. N7 |

| 5nm (N5P) | ? | +7 5 % vs. N5 | -10 % vs. N5 |

| 4nm (N4) | +6 % vs. N5 | téměř beze změny | beze změny |

| 4nm (N4P) | +6 % vs. N5 | +11 % vs. N5 +6 % vs. N4 | -22 % vs. N5 |

| 4nm (N4X) | ? | +15 % vs. N5 @1,2V +4 % vs. N4P @1,2V | ? |

| 4nm (N4C) | +8 % (?) | - (?) | - (?) |

| 3nm (N3) | +70 % vs. N5 2,9× vs. N7 | +10-15 % vs. N5 +32 % vs. N7 | -25-30 % vs. N5 |

| 3nm (N3B) | +60 % vs. N5 | +10-15 % vs. N5 +32 % vs. N7 | -35 % vs. N5 -43 % vs. N7(?) |

| 3nm (N3E 3-2 Fin) 3nm (N3E 2-2 Fin) 3nm (N3E 2-1 Fin) | +18 % vs. N5 +39 % vs. N5 +56 % vs. N5 | +33 % vs. N5 +23 % vs. N5 +11 % vs. N5 | -12 % vs. N5 -22 % vs. N5 -30 % vs. N5 |

| 3nm (N3P) | +4 % vs. N3E | +10 % vs. N3E | -5-10% vs. N3E |

| 3nm (N3S) | ? | ? | ? |

| 3nm (N3X) | +4 % vs. N3P | +15 % vs. N3P | ? |

| 3nm (N3A) | ? | ? | ? |

| 2nm (N2) | +10% vs. N3 +>15% vs. N3E | +13 % vs. N3E 2-1 +10-15 % vs. N3E | -33 % vs. N3E 2-1 -25-30 % vs. N3E |

| 2nm (N2P) | +9-13 % vs. N2? | +10-12 % vs. N2? | ? |

| 2nm (N2X) | ? | ? | ? |

| 1,6nm (A16) | +7-10 % vs. N2P +17-24 % vs. N2? | +6-10 % vs. N2P +17-23 % vs. N2? | -15-20 % vs. N2P |

| 1,4nm (A14) | ? | ? | ? |

TSMC A16

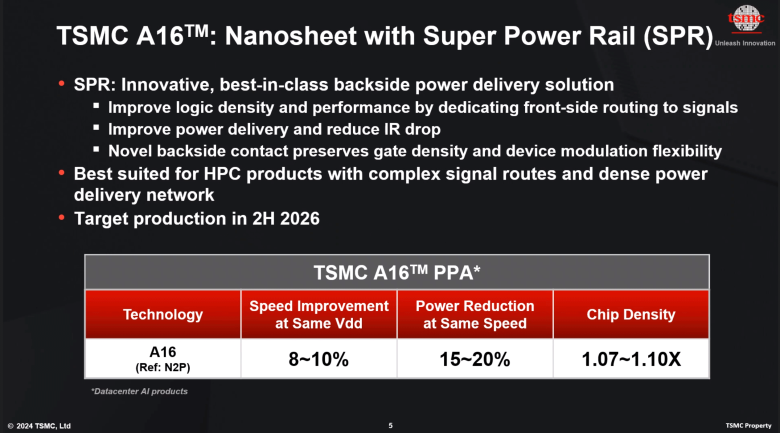

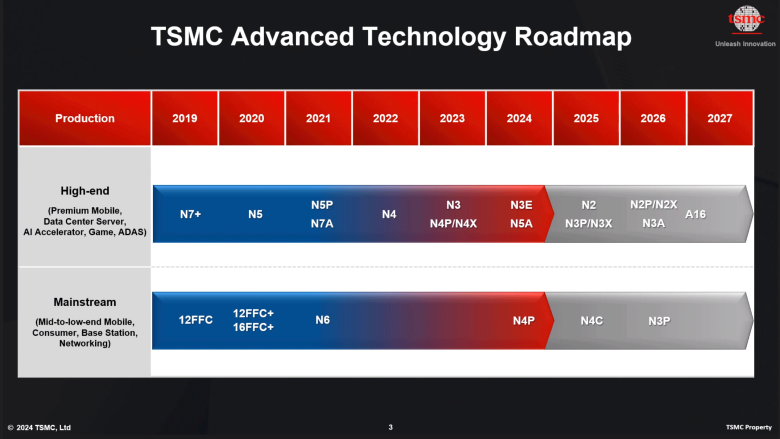

Oficiálně byl představen proces A16 (tzn. 1,6nm), který tedy bude prvním v nabídce TSMC s tzv. Backside Power Delivery. Společnost poněkud překvapivě srovnává specifikace s N2P (ač by se dalo očekávat spíše srovnání s N2, oproti němuž budou rozdíly větší a jehož nástupce fakticky je). Oproti N2P tedy stoupne denzita o 7-10 %, výkon o 6-10 % (při stejné spotřebě) a nebo klesne spotřeba o 15-20 % (při stejných taktech).

Hodnoty jsem do tabulky přepočítal i pro srovnání s N2 procesem, ale zůstává otázkou, zda je takové srovnání stále platné, protože není jasné, zda se s odstraněním Backside Power Delivery z procesu N2P nezměnily i jeho charakteristiky.

Proces A16 zakreslila TSMC do roadmapy šibalsky tak, že vypadá jako chystaný na konec roku 2026, ale pokud spustíme pomyslnou svislou čáru z konce chlívečku „2026“, zjistíme, že proces do tohoto chlívečku nezasahuje. Velkokapacitní výroba tedy začne počátkem roku 2027 (nebo - chcete-li - na přelomu roku 2026 / 2027), v roce 2026 to vypadá spíše na zkušební výrobu.

O procesu A14, který byl již párkrát neoficiálně zmíněn, zatím TSMC neprozradila nic konkrétního.