Více k Epyc Genoa: Téměř čtvercový socket, 12 čipletů, AVX3-512, BFLOAT16 aj.

Včera jsme si řekli, že Epyc Genoa přinese 96 jader / 192 vláken architektury Zen 4, vyráběný bude 5nm procesem, přinese dvanáctikanálový řadič s podporou DDR5-5200, 128 PCIe 5.0 linek a 320W TDP pro nejvýkonnější modely.

Pokud vás tato porce informací neuspokojila, můžete využít následující nášup:

Leaker Patrick Schur doplnil, že socket SP5 alias LGA-6096 bude téměř čtvercový. Šířka současného SP3 zůstane na 75,4 milimetrech, ale obdélník se posune podstatně blíže čtverci 58,5milimetrová strana se protáhne na 72 milimetrů.

Čtvercovitý (tedy blížící se čtverci) socket potvrdil i leaker ExecutableFix, který tvrdí, že zná konfiguraci, rozložení, rozměry a pozici čipletů. Na základě dostupných čísel vytvořil editací obrázku současného Epyc Milan / Zen 3 (vlevo) podobu Epyc Genoa / Zen 4, kterou vidíte v úvodu. Za povšimnutí stojí tři prvky.

(1) Centrální čiplet se výrazně zmenšil. Což znamená, že 12nm proces GlobalFoundries je ze hry a vcelku to eliminuje možnost nasazení 12nm+ procesu GlobalFoundries, neboť ten by podle všeho tak výrazné zmenšení nenabídl. Proslýchalo se nasazení 6nm procesu ovšem recentně jej dosud žádný leaker nepotvrdil. Alternativně lze uvažovat i o 8/10nm procesu Samsungu.

(2) Procesorových čipletů je 12, což znamená 8 jader na čiplet.

(3) Procesorové čiplety, přestože zůstávají osmijádrové, se nijak výrazně nezmenšily. 5nm proces zvyšuje denzitu o 80 %, ovšem čiplety jsou od pohledu jen mírně menší.

| ↓ komponenty ↓ | plocha | tranzistory |

| 12nm modul Zeppelin (Zen) | 212 mm² | 4,8 mld. |

| 7nm čiplet (Zen 2) | 74 mm² | 3,9 mld. |

| 7nm čiplet (Zen 3) | 80,7 mm² | 4,15 mld. |

| 5nm čiplet (Zen 4) | ~69 mm² | ~6,8 mld. |

| 12nm IO čiplet (Ryzen / Zen 2/3) | 125 mm² | 2,09 mld. |

| 12nm IO čiplet (Epyc / Zen 2/3) | 416 mm² | 8,34 mld. |

| ?nm IO čiplet (Epyc / Zen 4) | ~368 mm² | ? |

| ↓ produkty ↓ | ||

| Ryzen 1000 / 2000 | 212 mm² | 4,8 mld. |

| Ryzen 3000 6-8 jader | 199 mm² | 5,99 mld. |

| Ryzen 3000 12-16 jader | 273 mm² | 9,89 mld. |

| Epyc (Naples / Zen) | 848 mm² | 19,2 mld. |

| Epyc (Rome / Zen 2) | 1008 mm² | 39,54 mld. |

| Epyc (Milan / Zen 3) | 1062 mm² | 41,54 mld. |

| Epyc (Genoa / Zen 4) | 1196 mm² | ~90 mld. |

Protože autor tvrdí, že rozměry fotomontáže oproti Epycu Milan odpovídají poměrově i skutečnosti, můžeme snadno odvodit orientační rozměry nových čipletů. Jsou uvedeny v tabulce. Čiplet Zen 4 je nepatrně menší než čiplet Zen 2. Při parametrech 5nm procesu lze odvodit i hrubý počet tranzistorů (opět uvedeno v tabulce). Centrální čiplet je o 48 mm² menší, má zhruba 368 mm². Což kompenzuje spotřebu křemíku. 96jádrový Epyc Genoa tedy spotřebuje 1196 mm², což je jen o 13 % víc než 64jádrový Epyc Milan. 1,5× jader × 1,2× vyšší IPC = 1,8× vyšší výkon při 1,1× vyšší spotřebě křemíku. To se při omezených výrobních kapacitách jeví jako posun dobrým směrem.

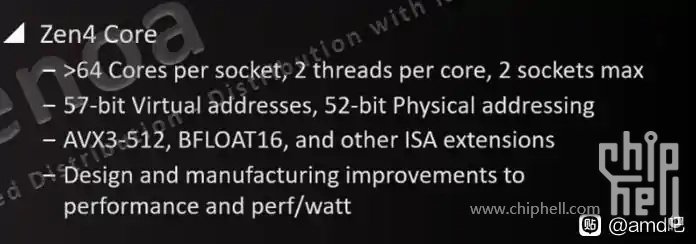

Odkudsi z hloubi diskuzního fóra ChipHell vyvstal kus slajdu, který uvádí podporu 57bit virtuálního adresování, 52bit fyzického adresování, podporu AVX3-512, BFloat16 a další rozšíření. O možnosti podpory AVX-512 se už v minulosti šuškalo, ale co je konkrétně AVX3-512, nemám příliš tušení.

Formát BFloat16 (dále BF16) vznikl jako řešení určené na míru světu akcelerátorů umělé inteligence, konkrétně DL, strojového učení (Deep Learning). Je důsledkem faktu, že většina hardwaru zvládá formát FP16 2× rychleji než FP32, respektive formát FP32 2× pomaleji než FP16 a ve chvílích, kdy FP16 nebyl dostatečně přesný (z hlediska výsledku) a bylo nutné přistoupit v k využití FP32, docházelo k degradaci výkonu.

Na BF16 můžeme nahlížet jako na formát, který vznikl z FP32 (32bit IEEE 754), který disponuje 8 bity pro dynamický rozsah (exponent) a 24 bity pro přesnost tohoto formátu (mantisa). BF16 zachovává 8 bitů dynamického rozsahu (exponent), ale přesnost formátu (mantisa) je snížena na 8 bitů. Z hlediska DL výpočtů není pro přesnost výsledků tolik důležitá přesnost formátu (mantisa) jako rozsah (exponent), takže výsledky výpočtů jsou podobně přesné jako při FP32, ale výkon je díky 16 bitům (8 bitů exponent + 8 bitů mantisa) podobný jako při použití FP16. Jde tedy o kompromis na míru.

Na úrovni výpočetních akcelerátorů podporuje AMD BF16 od architektury CDNA a akcelerátoru Instinct MI100. Zdá se, že na úrovni procesorů přijde podpora se Zen 4, tedy v roce 2022. V podpoře BF16 na úrovni procesorů je AMD časově o dva roky za Intelem, který ji přinesl v roce 2020. V praxi to ale není zásadní problém, neboť pro akceleraci náročných AI výpočtů se používají spíše specializované akcelerátory než x86 procesory a tam je AMD co do podpory BF16 pro změnu před Intelem.

Patrick Schur, ExecutableFix (1, 2), ChipHell