Více k V-cache aneb vrstvené L3 od AMD

Teplo

Když se s předstihem týdne začalo šuškat, že AMD plánuje nasadit vrstvené čiplety a vypadalo to právě na cache navrstvenou na čipletech, objevovaly se obavy uživatelů, jak to AMD vyřeší s teplem. V první řadě je potřeba říct, že křemík není nijak špatný vodič tepla, naopak se tepelnou vodivostí vyrovná leckerým kovům. Tepelná vodivost je závislejší na konkrétní teplotě než u většiny kovů, ale při teplotě, jaké v zátěži obvykle dosahují x86 procesory (podle různých zdrojů 120-175 W/m K) je vyšší než tepelná vodivost železa a srovnatelná se zinkem nebo mosazí.

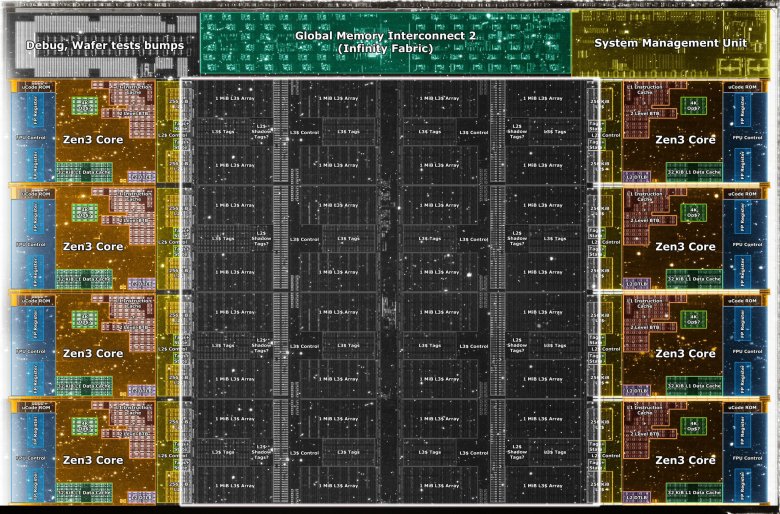

V případě demonstrovaného desktopového Ryzenu, kde je použito „jen“ 64 MB na čiplet, což odpovídá rozměrům 6×6 milimetrů, navíc vrstva cache nepřekrývá samotná x86 jádra. Níže jsem do popsaného snímku čipletu Zen 3 vyznačil (bílým rámem a bezbarvou plochou) plochu, která odpovídá navrstvené cache. Překrývá nativní L3 cache a část L2 cache - procesorová jádra cache nekryje:

Umístění berte ale spíš jako ilustraci. Je jasné, že situace není tak hezká, jak je namalováno na oficiálním slajdu v úvodu - čiplet má asi 7,3 milimetru na šířku a cache 6 milimetrů, takže cca 1,3 milimetru zůstává nepřekryto. Zda to odpovídá právě GMI rozhraní, jak jsem vyznačil na obrázku, není známo (dávalo by to ale celkem smysl).

Zbytek čipletu, aby z něj mohlo přecházet teplo na IHS a chladič, překryje křemík bez logiky. Mělo by jít o křemík upravený pro vyšší tepelnou vodivost, ale nic bližšího zveřejněno nebylo. Nelze však čekat, že tepelná vodivost tohoto křemíku bude nějak drasticky lepší - možná o pár desítek procent. Každopádně nic zásadního, co by znamenalo nějaký zlom. Osobně se domnívám, že u serverových procesorů (Milan-X), kde je výrazněji omezeno množství odpadního teplat na čiplet, nebude problém, pokud bude celý čiplet překryt (128MB) L3 cache.

Nemělo by jít o problém již z principu, neboť pro zachování výšky centrálního čipletu a celého pouzdra je pro x86 čiplety a navrstvenou L3 cache použit ztenčený křemík, takže výška celé křemíkové konstrukce (čiplet + navrstvená L3 cache) je stejná jako u soudobých nevrstvených čipletů. Tím pádem není vrstva křemíku, kterou musí teplo procházet, ani o desetinu milimetru vyšší než u aktuálních procesorů.

Význam

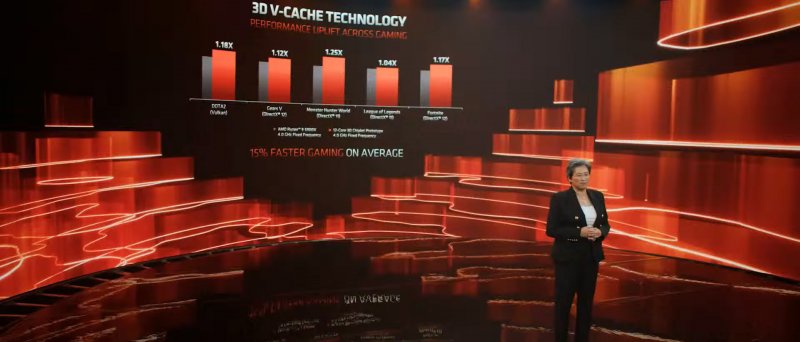

AMD se pochlubila prezentací herního výkonu, který obvykle z kapacity procesorové cache relativně dobře těží. Pokud jde o další typy úloh, kde by se cache mohla projevit, patří k hlavním kandidátům úlohy jako komprese dat. Komprese videa asi spíš méně, neboť ta je s ohledem na bloky využívající algoritmy navržena tak, aby se bloky vešly do standardní cache.

Celkově se ale dá širší uplatnění čekat v profesionální sféře, kde dochází ke zpracování daleko větších datových objemů. Úlohy, kde není možné data rozdělit na velmi malé bloky nebo toto rozdělení nese určitá omezení, by mohly vykazovat výrazný nárůst výkonu.

Pokud si uvědomíme, že AMD na 12jádrovém desktopovém modelu ilustrovala možnost výbavy herního procesoru 192MB paměti (L3 cache), nelze nostalgicky nevzpomenout na legendárního Diabla II, který pro slušný běh vyžadoval více než 128 MB operační paměti. Na demonstračním vzorku Ryzenu by se všechna potřebná data vešla do L3 cache a operační pamětí už by se uživatel nemusel trápit.

Uplatnění

AMD technologii demonstrovala na Ryzenu, desktopovém procesoru. Protože se pochlubila právě herním výkonem, dá se předpokládat, že desktopové Ryzeny vybavené touto cache budou sériově vyráběné a vydané. Rovněž ale víme (byť to na Computexu nebylo oficiálně potvrzeno; je možné, že si to AMD nechává na HotChips nebo jinou příležitost), že vrstvené čiplety využije také serverový Milan-X.

Bylo potvrzeno, že procesory s vrstvenou cache budou sériově vyráběné koncem letošního roku. AMD neuvedla výslovně, že půjde o desktopovou řadu, ale z kontextu (o jiné řeč nebyla) by to vyplývalo. Neoficiální zdroje hovořily o pravděpodobném vydání vrstveného Milan-X koncem roku, takže je možné, že pro servery bude technologie dostupná již ve čtvrtém kvartálu a desktop bude následovat krátce poté; k uvedení by mohlo dojít v lednu na CES 2022, což by zároveň byla reakce na Intel Alder Lake, jehož dostupnost se očekává koncem roku, asi v listopadu.

Krom desktopu a serverů se nabízí také úvahy o mobilním segmentu, což jsou primárně APU. Tam se ale podle leakera Bondrewd nasazení v-cache v dohledné době nechystá. To dává smysl, neboť už nyní se pro mobilní procesory používá ztenčená konstrukce a zvýšení by nebylo žádoucí. APU by v budoucnu měla být využita SLC cache, společnou cache pro CPU a GPU jádra. Ta patrně bude součástí základního křemíku a přijde snad v éře Zen 4.