Xeony Emerald Rapids 2,7× zvětšují L3 cache a vypovídají o problémech Intelu

Sapphire Rapids v kostce

Aktuálně vydané Xeony Sapphire Rapids byly velmi dlouhým, těžkým a komplikovaným porodem. Šlo o první dlaždicové řešení Intelu pro servery, kterého se po dlouho pokračující (a v podstatě marné) snaze vyrábět velké procesory jako monolity, dopustil. Problém byl, že si Intel rozložením na dlaždice situaci příliš neulehčil, protože zvolil extrémně složitý způsob jejich propojení, přičemž samotné jednotlivé dlaždice nebyly nijak podstatně menší než původní monolity. Starší revize Sapphire Rapids měla plochu dlaždice blízkou 400 mm², novější ji zmenšila na 377,5 mm². Celý Xeon Ice Lake nesl 628 mm² křemíku, takže plocha monolitické komponenty neklesla ani na polovinu.

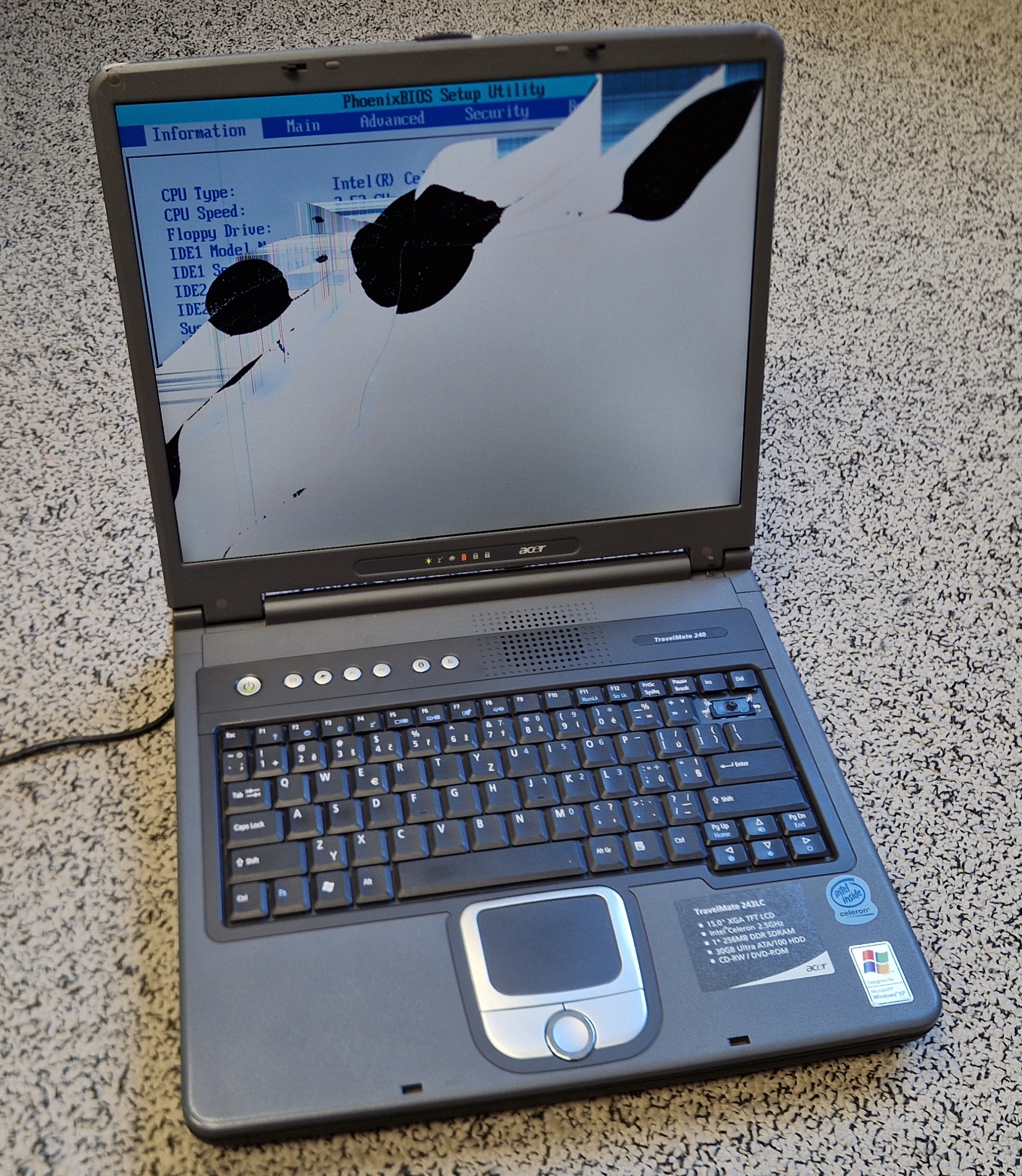

dlaždice Sapphire Rapids

Připomeňme, že Sapphire Rapids se skládá ze čtyř shodně vybavených dlaždic. Každá nese fyzicky 15 procesorových jader. Původně měla jít na trh nanejvýš konfigurace s 56 aktivními jádry (tzn. v každé dlaždici by bylo jedno vypnuté), ale s ohledem na (více)generační výkonnostní skluz nakonec Intel uvedl alespoň jeden model s plnými 60 jádry. Jednotlivé dlaždice jsou totožné co do výbavy a návrhu, pouze jsou opticky převrácené, aby je bylo možné snáze sesadit a propojit. K tomu slouží EMIB (propojovací můstky), kterých Sapphire Rapids potřebuje celkem 10 (navzdory zjednodušující grafice Intelu malující čtyři).

Emerald Rapids

Emerald Rapids byl od počátku chápán jako Sapphire Rapids-refresh. Stejná architektura s o ~10 % vyšší počtem jader, optimalizacemi a zvětšenou cache nedává prostor pro nějaký významnější posun výkonu a nedá se tudíž čekat, že by tato řada mohl výrazněji zlepšit konkurenční pozici Intelu.

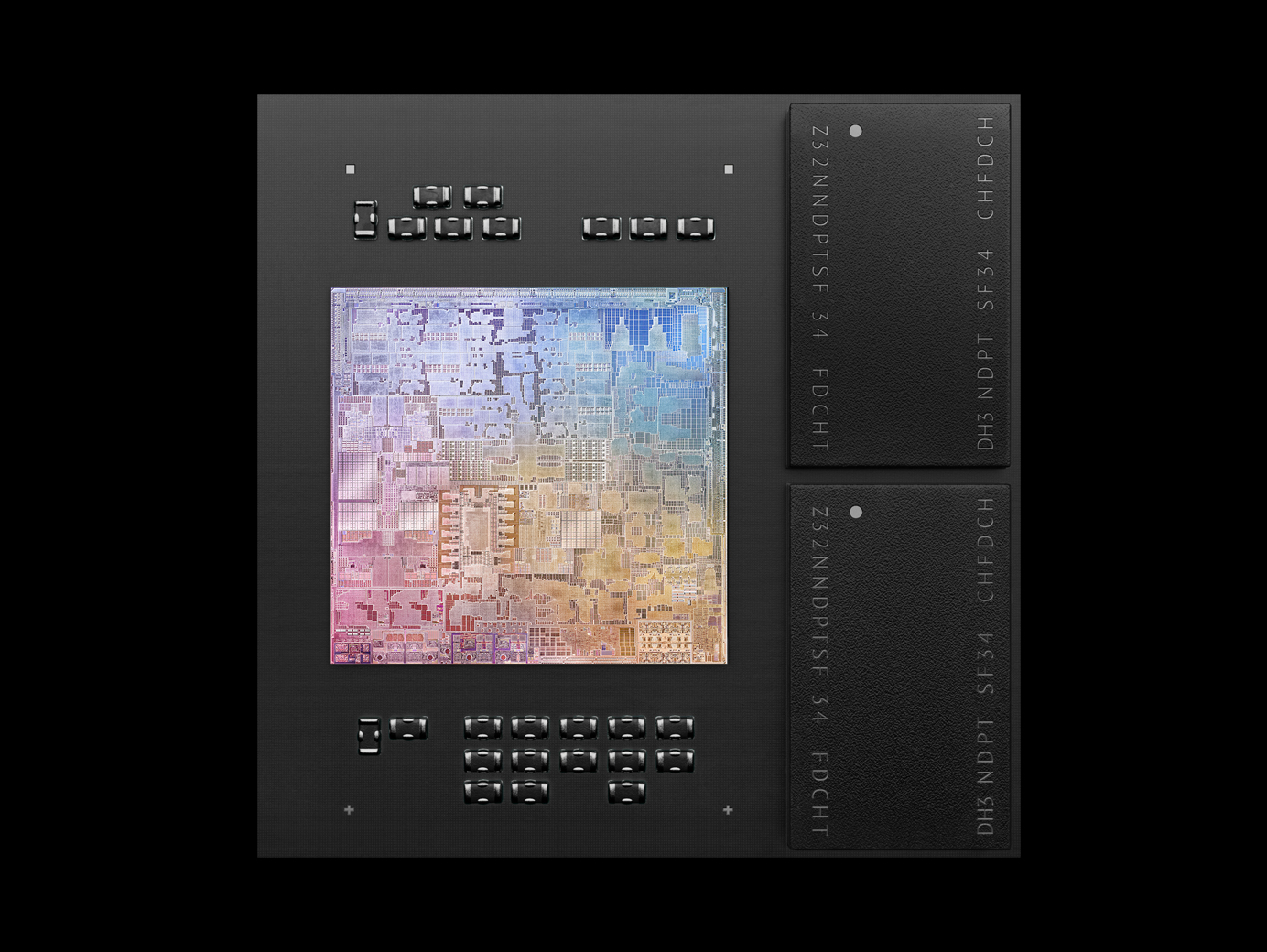

zdroj: SemiAnalysis

Nyní se však ukazuje, že (navzdory počtu jader a očekávatelné konkurenceschopnosti) je Emerald Rapids po stránce návrhu poměrně výraznou změnou. Ne, na architektuře x86 jader se nic nemění, ale mění se toho poměrně dost okolo. Začněme u toho, co je jádru nejbližší a to cache. L3 cache u Sapphire Rapids byla 1920kB pro každé jádro. Emerald Rapids kapacitu navýší na 5120 kB, tj. 2,67×. Dále se velmi výrazně měnší struktura procesoru. Již nepůjde o 4 dlaždice s plochou 377,5 mm² pro každou, ale jen(!) 2 dlaždice s plochou 746,5 mm² pro každou. To znamená, že se dlaždice velmi výrazně zvětší a to nad úroveň monolitického Xeonu Ice Lake (628 mm²) i monolitického Xeonu Skylake (694 mm²).

zdroj: SemiAnalysis

Z toho vyplývá, že po zkušenosti se Sapphire Rapids vidí Intel jako schůdnější vrátit se k velkým kusům křemíku (>600 mm²) než řešit rychlý, ale patrně extrémně náročný systém propojení více dlaždic přes vysoký počet můstků (EMIB).

Vlevo 33j. dlaždice Emerald Rapids (Semi Analysis), vpravo loni prezentovaný 34j. křemík (Angstronomics)

Každá (z obou) dlaždic nese 33 jader, což znamená 66 jader pro celý procesor, z čehož se počítá s 32 aktivními jádry na dlaždici a 64 jádry procesoru celkem. Hodnota 33 jader nápadně připomíná 34jádrový křemík, který Intel ukázal loni na podzim (dosud nebylo jasné, co tím chtěl Intel říci). Nyní to vypadá, že mohlo jít o jednu ze zvažovaných konfigurací, jejíž vývoj pokračoval v 33jádrovou dlaždici.

Dlaždice se však neliší jen počtem jader. 34jádrová konfigurace nesla 1920kB cache (na jádro) jako Sapphire Rapids, ale na druhé straně byla vybavena dvojnásobkem DDR5 kanálů. 33jádrová konfigurace nese 5120kB cache, ale má polovinu DDR5 kanálů. Větší cache zjevně kompenzuje užší paměťové rozhraní. Mohlo by tak jít o optimalizaci ceny platformy.

| dlaždice Emerald Rapids | křemík z podzimu 2022 | |

|---|---|---|

| jader | 33 | 34 |

| L3 cache na j. | 5120 kB | 1920 kB |

| DDR5 rozhraní (160bit) | 2× (4 kanály) | 4× (8 kanálů) |

| PCIe ×16 | 3× | 5× |

| akcelerátory | 2× | 2× |

| EMIB PHY | ano | pravděpodobně ne |

Podstatným rozdílem pak je, že na křemíku z loni prezentovaného waferu chybí cokoli, co by zjevně připomínalo EMIB rozhraní, takže mohlo jít buďto o testovací čip, nebo variantu určenou pro systémy s nižším počtem jader.