Zen 6 APU počítají s 2nm i 3nm procesem, portfolio je masivní

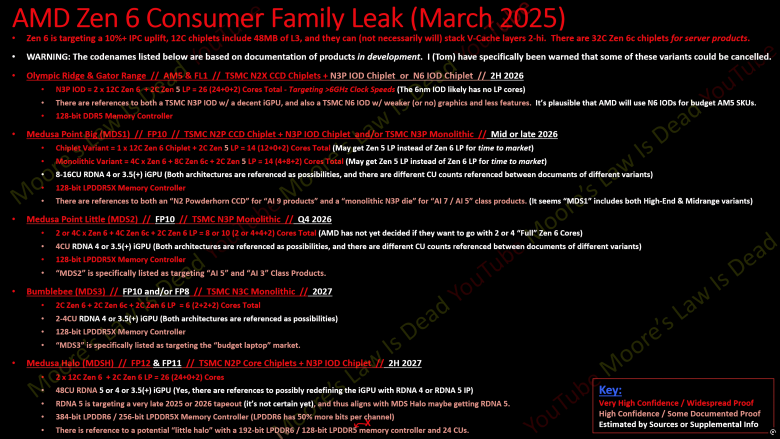

V pátek jsme se podívali na plány AMD s architekturou Zen 6 pro klasická CPU, nyní jsou na řadě APU. V případě APU je situace komplikovanější a méně přehledná. Dokumenty totiž obsahují řadu různých modelů a je možné, že některé z nich nakonec na trh nedorazí.

Jako u dosavadních generací tak i v případě Zen 6 v rámci řady klasických APU existuje větší (Medusa Point 1) a menší (Medusa Point 2) verze. Větší APU však existuje ještě v dalších dvou variantách – výkonnější a pokročilejší čipletové, jejíž procesorová jádra vznikají na 2nm (N2P) procesu TSMC a o něco méně výkonné monolitické, která je celá vyrobena 3nm (N3P) procesem TSMC.

Medusa Point 1 - čipletový

Čipletová verze Medusa Point 1, říkejme jí Ryzen 9, tedy ponese 2nm (N2P) CCD s 12 jádry Zen 6, 3nm (N3P) IOD s integrovanou grafikou o 16 CU RDNA 3.5 nebo RDNA 4 (navzdory tomu, že některé zdroje hovoří o jedné a jiné o druhé, to vypadá, že ve skutečnosti nepadlo definitivní rozhodnutí a nejspíš bude záležet na to, co se do uzavření návrhu stihne). IOD dále obsahuje dvě úsporná (LP) jádra Zen 5 nebo Zen 6 určená na klidový provoz. Opět není jisté, zda se stihne dokončit návrh Zen 6-LP a aktuálně vypadá jako pravděpodobnější scénář využití Zen 5-LP. Vydání lze očekávat ve třetím kvartálu 2026, pokud vše půjde dobře.

Medusa Point 1 - monolitický

Monolitická verze Medusa Point 1, patrně určená pro Ryzen 7 a Ryzen 5, vznikne jako celek na 3nm procesu (N3P). Ponese 4× Zen 6, 8× Zen 6c a opět 2× Zen 5 LP (nebo Zen 6 LP) pro klidový provoz. Integrovaná grafika disponuje 8 CU RDNA 3.5 nebo RDNA 4.

Medusa Point 2

Medusa Point 2, menší APU, vznikne výhradně jako monolit. Podobně jako u současné generace bude vydané později, podle MLID snad ve čtvrtém kvartálu 2026, ale osobně bych očekával spíš CES 2027 (na který by jinak prakticky nic nezbylo). Ponese 2-4× Zen 6, 4× Zen 6c a 2× Zen 6 LP pro úsporný provoz (s ohledem na pozdější vydání již bude Zen 6 LP zcela jistě hotový a nebude důvod zůstávat u Zen 5 LP). Grafické jádro bude vybaveno zhruba 4 CU RDNA 3.5 nebo RDNA 4 (počet funkčních jednotek není definitivně uzavřen). Cílem jsou procesory Ryzen 5 a Ryzen 3.

Bumblebee

Bumblebee je nejmenší APU, tedy produkt pro segment, který AMD neaktualizuje v každé generaci. Opět půjde o monolit vyrobený na 3nm procesu TSMC, ale tentokrát na levnější variantě N3C. Základem bude 2× Zen 6, 2× Zen 6c a 2× Zen 6 LP, tedy 6 jader celkem. Grafiku obstarají 2-4 CU RDNA 4 nebo 3.5. Cílem jsou levnější notebooky v roce 2027.

Medusa Halo

Medusa Halo je velké čipletové APU, nástupce Strix Halo. Již o něm byla řeč. Ponese 2× 12 jader Zen 6 (stejné čiplety jako Medusa Point 1). Grafika je projektována na 48 CU (3072 EU), ovšem v úvahu údajně připadají všechny možnosti od RDNA 5 až po RDNA 3.5. Na papíře existuje varianta s 256bit LPDDR5X řadičem a s 384bit LPDDR6 řadičem. Vzhledem k rychlejším pamětem na 384bit rozhraní by tato verze měla nabízet téměř 2× vyšší paměťovou propustnost než 256bit verze. Podobně jako u současné generace existuje na papíře i levnější verze Medusa Halo, která se liší poloviční grafikou (24 CU) a užší sběrnicí (192bit LPDDR5X). S řadou Halo se alespoň podle stávající plánů počítá až na 2. polovinu roku 2027, což je možná trochu škoda. AMD se tím připravuje o příležitost vydat ji jako konkurenta Blackwellu, neboť ve druhém pololetí již dost možná bude v mobilním segmentu dostupný jeho nástupce.

| x86 jader | Zen 6 | Zen 6c | Zen 5/6 LP | RDNA CU | sběrnice | |

|---|---|---|---|---|---|---|

| Olympic Ridge (AM5) | 24(-26) | 24 | - | 0-2 | 2? | 128bit |

| Gator Range (FL1) | 26 | 24 | - | 2 | 4? | 128bit |

| Medusa Halo | 26 | 24 | - | 2 | 48 | 256-384bit |

| Medusa Halo LP | 14? | 12? | - | 2? | 24 | 192bit |

| Medusa Point 1 čiplet | 14 | 12 | - | 2 | 16 | 128bit |

| Medusa Point 1 monolit | 14 | 4 | 8 | 2 | 8 | 128bit |

| Medusa Point 2 | 8-10 | 2-4 | 4 | 2 | 4? | 128bit |

| Bumblebee | 6 | 2 | 2 | 2 | 2-4 | 128bit |

Výrobní procesy Zen 6

Pokud si shrneme, o kterých výrobních procesech v souvislosti se Zen 6 byla řeč, vychází to na:

- N2X - nejrychlejší proces určený pro CCD čiplety klasických CPU

- N2P - výkonný proces určený pro CCD čiplety APU

- N3P - výkonný proces určený pro monolitická APU a IOD čiplety APU + CPU

- N3C - levnější proces určený pro levnější monolitická APU

- 4LPP - proces Samsungu, u kterém se mluvilo v souvislosti s IOD čiplety serverových CPU

- N6 - proces zmiňovaný v souvislosti s IOD čiplety CPU

Jen z dosavadních informací vyplývá, že na Zen 6 produktech se může podílet 6 různých výrobních procesů dvou výrobců. Důvodem pro tak značnou diverzifikaci může být snaha maximalizovat dostupné výrobní kapacity. Připomeňme, že AMD v poslední době stoupl tržní podíl v segmentu x86 procesorů, ale v situaci, kdy téměř všechny produkty společnosti (desktopová CPU, APU, akcelerátory i GPU) využívají stejnou technologii (TSMC N4/N4P) jsou výrobní kapacity omezené, neboť kapacity 4nm linek TSMC nejsou nekonečné.