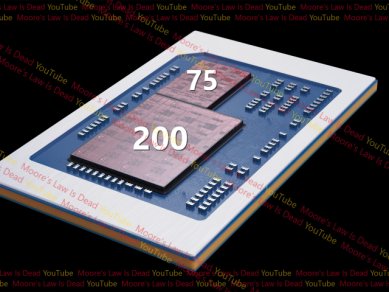

Zen 6 pro PC vznikne u TSMC, CCD má 75 mm², GCD 155 mm², u APU 200 mm²

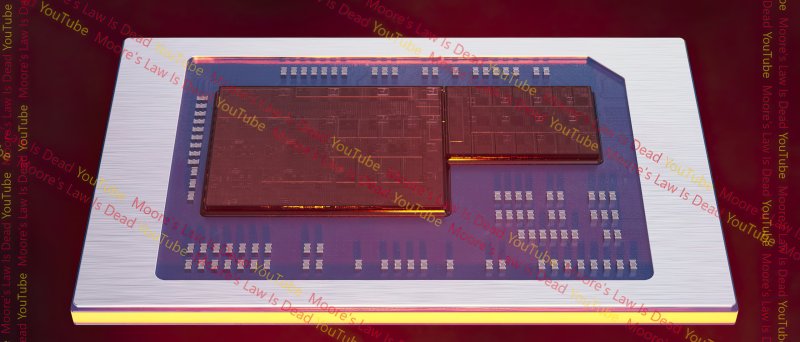

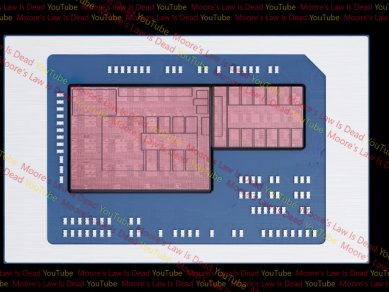

YouTube kanál MLID zveřejnil velké množství informací o čipletové architektuře procesorů postavených na architektuře Zen 6, které budou určené pro osobní počítače. Nechybí ani rendery založené na technických nákresech a specifikacích. AMD připravuje klasické řešení primárně určené pro desktop (kompatibilita s AM5 socketem zůstává v platnosti), které se bude jmenovat Olympic Ridge, a APU pro notebooky nazvané Medusa Point. Oba produkty mají společný CCD (procesorový) čiplet s 12 jádry Zen 6, který měří zhruba 75 mm².

Olympic Ridge = (2×) 75 mm² CCD + 200 mm² IOD

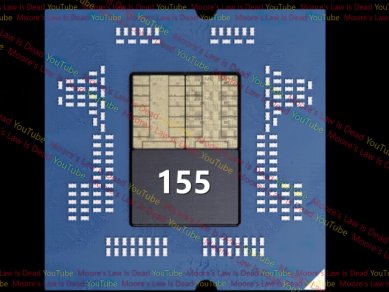

CPU Olympic Ridge bude disponovat jedním až dvěma CCD a jedním IOD (centrálním čipletem) o ploše asi 155 mm².

| ↓ komponenty ↓ | plocha | tranzistory |

|---|---|---|

| 12nm modul Zeppelin (Zen) | 212 mm² | 4,8 mld. |

| 7nm čiplet (Zen 2) | 74 mm² | 3,9 mld. |

| 7nm čiplet (Zen 3) | 80,7 mm² | 4,15 mld. |

| 5nm čiplet (Zen 4) | 71 mm² | 6,57 mld. |

| 5nm čiplet (Zen 4c) | 72,7 mm² | ~8,85 mld. |

| 4nm čiplet (Zen 5) | 70,6 mm² | 8,315 mld. |

| 3nm? čiplet (Zen 6) | ~75 mm² | ? |

| 12nm IO čiplet (Ryzen / Zen 2/3) | 125 mm² | 2,09 mld. |

| 12nm IO čiplet (Epyc / Zen 2/3) | 416 mm² | 8,34 mld. |

| 6nm IO čiplet (Ryzen / Zen 4/5) | 122 mm² | 3,37 mld. |

| 6nm IO čiplet (Epyc / Zen 4) | 396,6 mm² | ~11,2 mld. |

| 4nm? IO čiplet (Zen 6) | 155 mm² | ? |

| ↓ produkty ↓ | ||

| Ryzen 1000 / 2000 | 212 mm² | 4,8 mld. |

| Ryzen 3000 6-8 jader | 199 mm² | 5,99 mld. |

| Ryzen 3000 12-16 jader | 273 mm² | 9,89 mld. |

| Ryzen 5000 6-8 jader | 206 mm² | 6,24 mld. |

| Ryzen 5000 12-16 jader | 286 mm² | 10,4 mld. |

| Ryzen 7000 6-8 jader | 193 mm² | 9,9 mld. |

| Ryzen 7000 12-16 jader | 264 mm² | 16,5 mld. |

| Ryzen 9000 6-8 jader | 193 mm² | 11,7 mld. |

| Ryzen 9000 12-16 jader | 263 mm² | 20 mld. |

| Ryzen „10k“ 6-12 jader | 230 mm² | ? |

| Ryzen „10k“ 16-24 jader | 305 mm² | ? |

| Epyc (Naples / Zen) | 848 mm² | 19,2 mld. |

| Epyc (Rome / Zen 2) | 1008 mm² | 39,54 mld. |

| Epyc (Milan / Zen 3) | 1062 mm² | 41,54 mld. |

| Epyc (Genoa / Zen 4) | 1249 mm² | 90,2 mld. |

| Epyc (Bergamo / Zen 4c) | 978 mm² | 82 mld. |

| Epyc (Siena / Zen 4c) | 687 mm² | 47 mld. |

Jak sami vidíte, stoupla plocha CCD (zhruba na úroveň Zen 2, ale stále pod 81mm² Zen 3). Podstatně výrazněji však stoupla plocha IOD, který v současnosti dosahuje asi 122 mm², zatímco s příští generací naroste na 155 mm². Co konkrétně plochu tak výrazně navýší, není jasné. Pravděpodobným kandidátem je NPU, možná přítomnost několika céčkových jader pro úsporu energie a posledním hypotetickým kandidátem je širší konektivita.

Procesor Olympic Ridge: 2× 12jádrový Zen 6 CCD + IOD (MLID)

MLID spekuluje o větším integrovaném GPU, které by mělo potenciál na úrovni současných APU, ale osobně pochybuji, že by to AMD něco konkrétního přineslo. Kdo má zájem o řešení s výkonnější integrovanou grafiku, pro toho jsou APU. V mobilním segmentu jsou pak výkonné procesory prakticky vždy párovány se samostatnými grafikami.

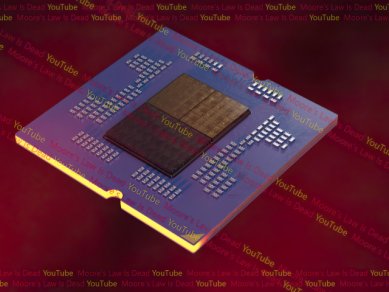

Medusa Point = 75 mm² CCD + 225 mm² IOD

| APU | rok | proc. | CPU | GPU (SP) | plocha |

|---|---|---|---|---|---|

| Llano | 2011 | 32nm | 4/4× K10,5 | 400 VLIW-5 | 226 mm² |

| Trinity Richland | 2012 2013 | 32nm | 4/4× Piledriver | 384 VLIW-4 | 246 mm² |

| Kaveri | 2014 | 28nm | 4/4× Steamroller | 512 GCN 2 | 245 mm² |

| Carrizo Bristol Ridge | 2015 2016 | 28nm | 4/4× Excavator | 512 GCN 3 | 245 mm² |

| Raven Ridge Picasso | 2017 2019 | 14nm 12nm | 4/8× Zen(+) | 704 Vega | 210 mm² |

| Renoir Lucienne | 2020 2021 | 7nm | 8/16× Zen 2 | 512 Vega+ | 156 mm² |

| Cezanne Barcelo | 2021 2022 | 7nm | 8/16× Zen 3 | 512 Vega+ | 180 mm² |

| Rembrandt | 2022 | 6nm | 8/16× Zen 3+ | 768 RDNA 2 | 208 mm² |

| Phoenix Phoenix 2 | 2023 | 4nm | 8/16× Zen 4 2+4/12× Zen 4(c) | 768 RDNA 3 256 RDNA 3 | 178 mm² 137 mm² |

| Strix Point Kraken | 2024 2025 | 4nm | 4+8/24× Zen 5(c) 4+4/16× Zen 5(c) | 1024 RDNA 3.5 512 RDNA 3.5 | 225 mm² 170 mm² |

| Strix Halo | 2025 | 4nm | 16/32× Zen 5 | 2560 RDNA 3.5 | 380 mm² |

| Medusa Point | 2027 | 3nm | 12× Zen 6 | 1024 UDNA | 275 mm² |

APU Medusa Point kombinuje jedno CCD a jedno větší IOD o ploše 200 mm². Dostáváme se tedy na plochu 275 mm², což je s výjimkou aktuálně vydávaného Strix Halo s přehledem největší APU od AMD. Nejen co se týče éry Zenu, ale o ~30 mm² překonává i produkty éry stavebních strojů. Je jasné, že o pár milimetrů navíc si řeknou větší x86 jádra a rozhraní k propojení čipletů. To jsme ale stále jen na řekněme 10-15 mm². Kam půjde zbytek?

APU Medusa Point: 12jádrový Zen 6 CCD + IOD (MLID)

Už jsme něco slyšeli o tom, že má podstatně narůst NPU (AI akcelerátor). Integrovaná grafika asi zůstane na 1024 stream-procesorech, ale o generaci a půl poskočí architektura, tedy bude potřeba doplnit tranzistory generace RDNA 4 i UDNA.

Další plochu si nejspíš vezme Infinity Cache, která měla být původně v podobě 16MB kapacity přítomná již na APU Strix Point, ale z důvodu požadavku Microsoftu na výkonnější NPU musela uvolnit místo. Nyní by NPU mohla přinést výkonnostní bonus k 1,5generačnímu architektonickému upgradu. Posledním prvkem, který se na ploše IOD mohl podepsat, jsou opět x86 jádra pro snížení energetických nároků.

Pouzdření a propojení

Zásadní změnou oproti všem předchozím čipletovým řešením AMD pro osobní počítače s výjimkou Strix Halo je spojení čipletů a pouzdření. Dosavadní řešení spočívalo v tom, že každý čiplet byl vybaven GMI rozhraním, které bylo z křemíku vyvedeno do pouzdra a odtud vycházelo do GMI rozhraní sousedního kusu křemíku. Rozhraní vedoucí přes substrát pouzdra nemohlo být (datově) příliš široké a zároveň muselo běžet na vyšších taktech, aby zajišťovalo dostatečnou přenosovou rychlost. Jeho výhodou byly velmi nízké výrobní náklady, nevýhodou pak vyšší latence a určité energetické nároky.

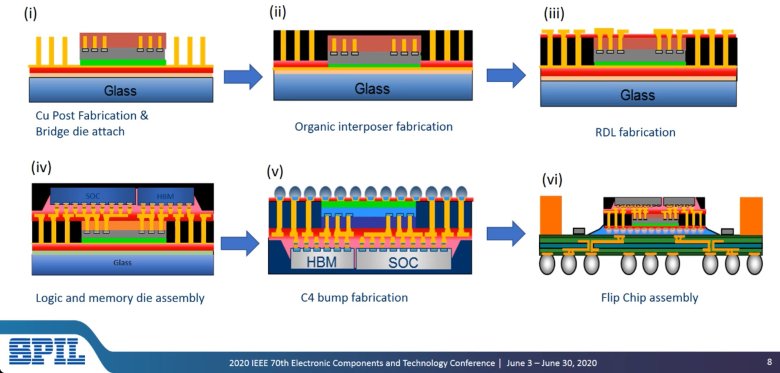

Všechny procesory s architekturou Zen 6 již budou využívat spojení křemík-křemík. Přinejmenším v případě PC varianty bude realizované křemíkovými můstky, které vyrobí společnost UMC. Menším překvapením je, že samotné pouzdření nebude zajišťovat TSMC. AMD oslovila tchajwanský SPIL, který použije technologii FOEB (Fan-out Embedded Bridge).

Proces implementace SPIL FOEB - v případě Zen 6 však nebudou propojovány HBM a SOC, ale CCD a IOD; princim však zůstává stejný (SPIL)

To s sebou nese dvě výhody. Tou první je, že pouzdřením mimo TSMC nebude AMD přicházet o (omezené) pouzdřící kapacity na technologiích používaných pro AI akcelerátory. Jinými slovy, AI akcelerátory a PC procesory se nebudou přetahovat o pouzdřící kapacity. Druhá výhoda tkví v tom, že AMD sice mohla i mimo TSMC sáhnout po nějaké jiné technologii a dodavateli - většina by však při požadovaných kapacitách nejspíš nabídla pouze řešení postavené na křemíkové podložce (interposer), které je při stávajících cenách křemíku nákladnější. Pokud bude SPIL v příštím roce schopný pouzdřit technologií FOEB objemy, které AMD potřebuje k pokrytí PC segmentu, pak se tato volba jeví jako výhra.

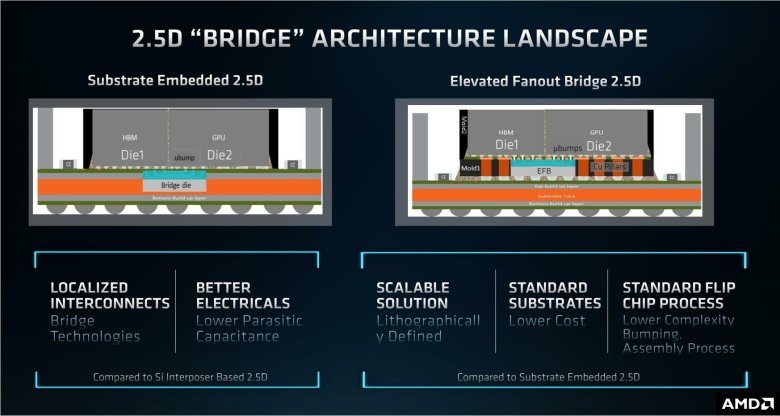

Závěrem si ještě zasluhuje opravit jedna nepřesnost uvedená MLID. Ten hovoří, že můstek bude zanořený do „base die“, tedy do křemíkové základny. FOEB ve skutečnosti žádnou base die nevyužívá, přítomna je jen organická struktura, která zvedá čiplety, aby vytvořila prostor pro můstek (a kterou procházejí měděné spoje).

FOEB oproti klasickému řešení můstku zanořeného do substrátu nabízí ještě několik dalších výhod. První jsou požadavky a náklady na pouzdření hotového slepence na úroveň finálního pouzdra.

Srovnání můstku zanořeného do substrátu (vlevo) a můstku v navýšené konstrukci (vpravo) (AMD)

Zatímco při použití zanořeného můstku je zapotřebí i zde speciální pouzdřící technologie (právě proto, aby mohl být můstek do pouzdra zanořen), v případě FOEB lze křemíkový slepenec umístit na standardní pouzdro (Flip Chip), protože se do pouzdra samotného nic nezanořuje, vše leží na jeho povrchu, jako kdyby se pouzdřilo monolitické řešení. Oproti zanořenému můstku se také používají standardní pouzdřící substráty. Existují i další výhody, jako snazší škálovatelnost

MLID, SPIL aj.