2nm proces TSMC využije nanosheets, do budoucna se zvažuje CFET

O technologii GAA (Gate All-Around) se mluví nejdéle ve spojitosti se společností Samsung, která její derivát nazvaný MBCFET využívá v 3nm výrobě (původně jej chtěla nasadit už dříve, na 4nm). Tuto myšlenku ale plánují využít i další výrobci a byť ji nazývají odlišně, jde v podstatě o variace na MBCFET, tedy „pásky“, nikoli generické „dráty“, které se objevovaly ve starších prezentacích o GAA.

Víme, že Intel této technologii říká RibbonFET a chce ji uvést do sériové výroby v roce 2024 s procesem Intel 20A. Zvažovala ji i TSMC, která potvrdila, že ji nasadí na 2nm procesu (poslední oficiální informace ohledně zahájení velkokapacitní výroby se týkaly druhého pololetí 2025 s experimenty od čtvrtého kvartálu 2024). Ta (více-méně) tutéž technologii označuje termínem Nanosheet(s).

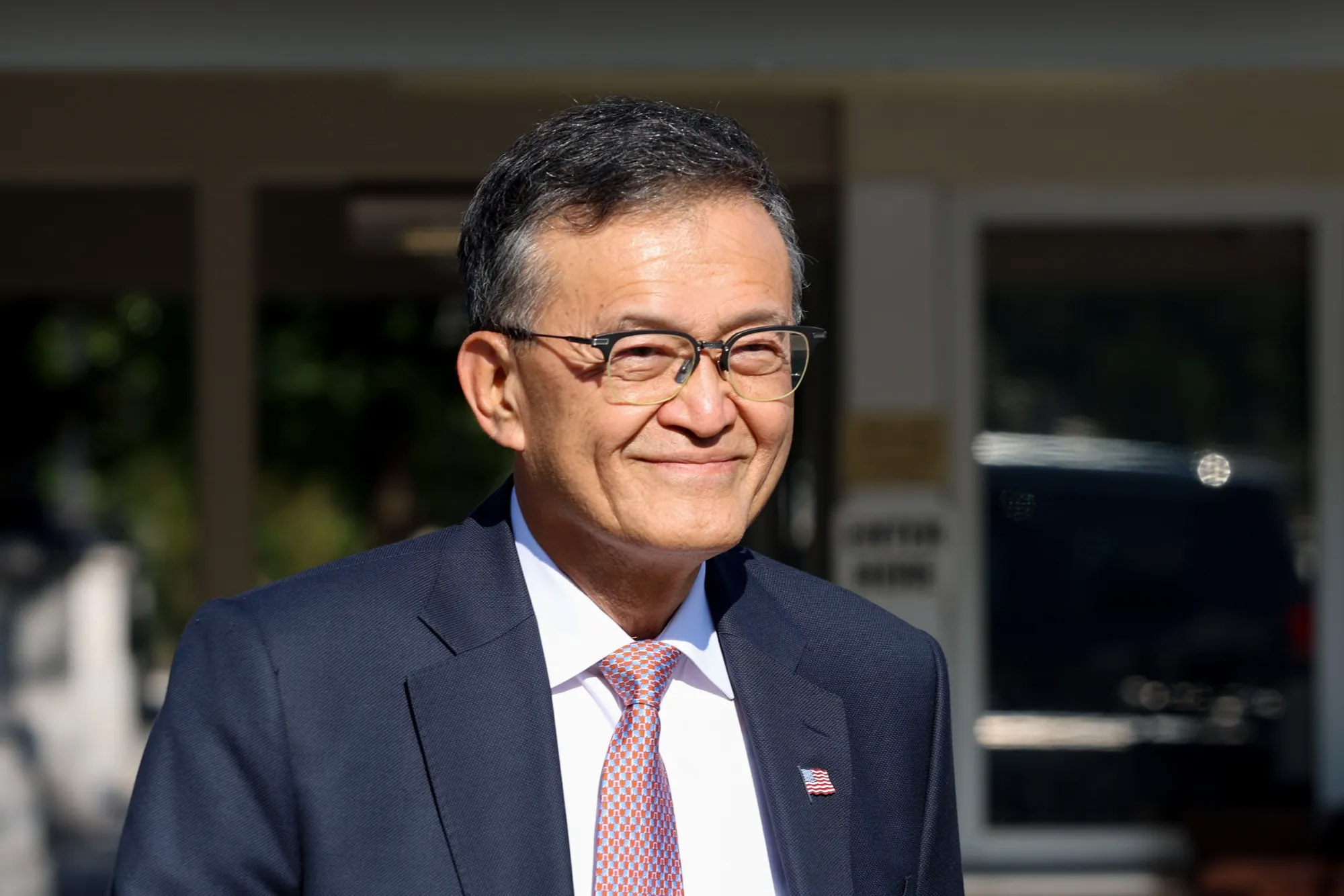

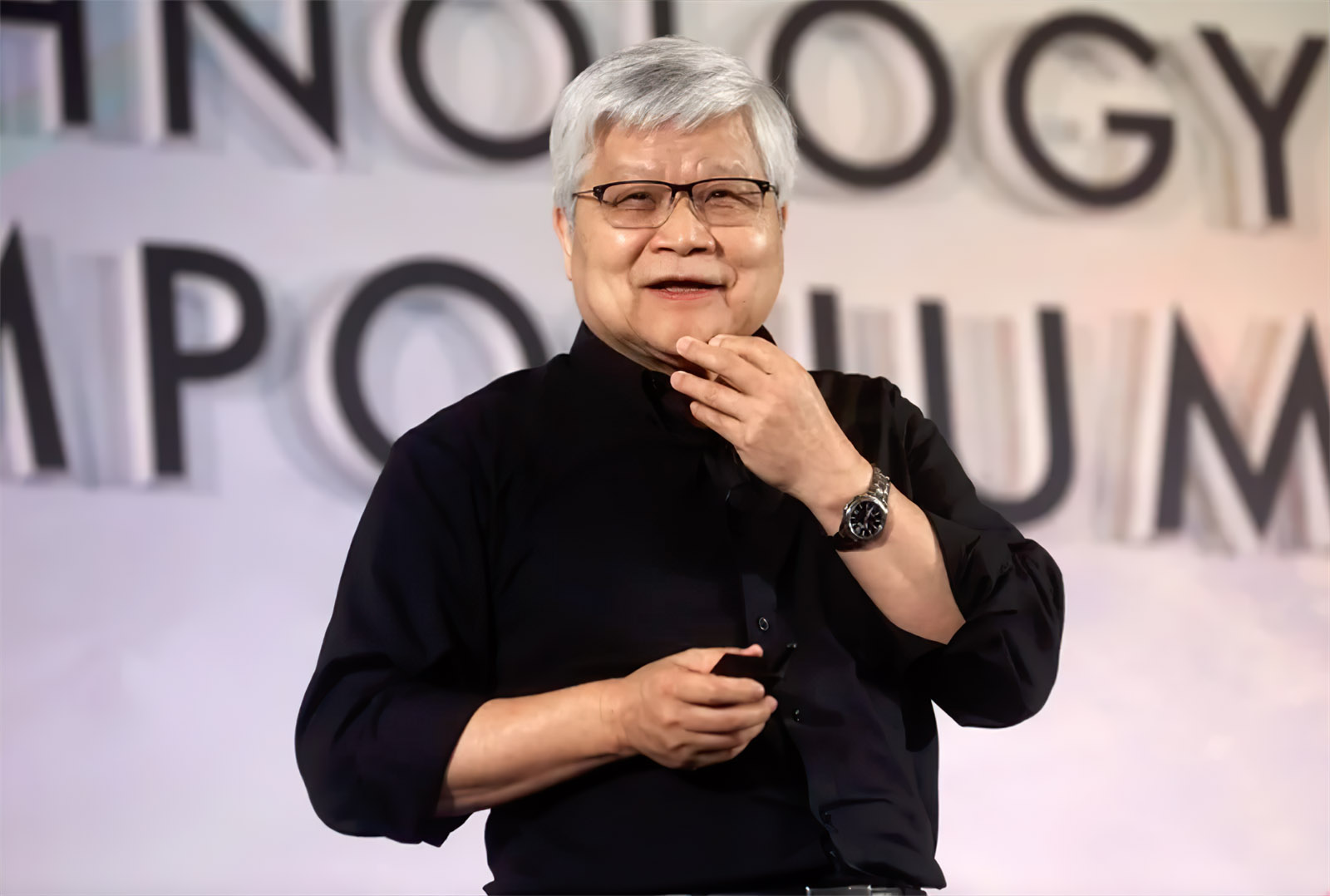

TSMC již ale uvažuje i o tom, co použít po Nanosheets. Jednou z možností (sama zdůrazňuje, že skutečně možností), je tzv. CFET. Jejím cíle by bylo (za účelem zvýšení denzity tranzistorů) navrstvit polovodiče typu P a polovodiče typu N přímo na sebe. Technolofie CFET je zatím ve fázi vývoje a vice-prezident TSMC Kevin Zhang potvrdil, že jde o jednu z (více) možností. Pravděpodobně však tu, od které si společnost slibuje nejvíce nebo její implementaci vidí jako nejschůdnější, neboť právě tu si Zhang vybral k prezentaci.

Pokud plány největších výrobců dopadnou, jak si zatím tyto firmy slibují, pak jako první bude (respektive je) Samsung, v roce 2024 bude následovat Intel a v roce 2025 TSMC. Nutno však dodat, že Samsung s MBCFET spíše zákazníky ztratil než získal, neboť při kombinaci v posledních letech nízké výtěžnosti zapůsobilo relativně rané nasazení nové nevyzkoušené technologie jako strašák na zákazníky, kteří dali přednost TSMC.