Údajné specifikace GPU Hawaii jsou jen špatně opsanými spekulacemi

3D Center, stejně jako činí po léta, i před vydáním čipu Hawaii posbíral po internetu potvrzené informace o novém GPU. Co není známo, doplnil vlastními (byť rozumnými) spekulacemi a výsledek vydal. Můžeme si jen domýšlet, zda je problémem jazyková bariéra (3D Center píše německy), nebo lenost číst/překládat i text kolem údajů, či snad snaha o vyrobení senzace - opět se našlo pár webů, které tyto spekulace vydávají za „uniklé parametry“.

Mezi ně letos patří například i TweakTown. Ten nejen že nepochopil podstatu informací, ale navíc údaje ani správně neopsal, takže kde německý zdroj hovoří o rozsahu „maximálně 2816 a minimálně 2304 stream-procesorů“, předkládá TweakTown jako hotovou věc nejvyšší hodnotu uvedeného rozsahu.

Předpoklady 3D Center se poměrně blízce shodují s našim očekáváním z poloviny srpna (kdy jsme vyvraceli tehdejší šílenou hypotézu o 3840 stream-procesorech), takže se jim samotným nemá smysl věnovat - pouze bychom se opakovali.

Byť od té doby uteklo pět týdnů, víme jen o málo víc. Jednak to je informace, že čip bude dosahovat více než 420 mm² (ale asi nepřesáhne 440 mm²) - tu jsme si už rozebrali v samostatném článku. Dále pak bylo oficiálně potvrzeno, že na 25. září (příští týden ve středu) chystá AMD oficiální představení, které bude živě streamovat na svém webu i na YouTube. Takový způsob odhalení není zrovna obvyklý. Je otázkou, kolik toho společnost prozradí; jsou-li totiž zprávy z jiných zdrojů správné, nedostane se karta do obchodů dříve než v říjnu.

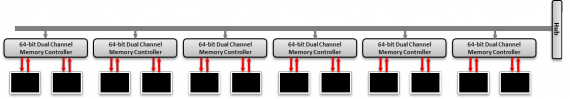

384bit řadič GPU Tahiti zásobuje šest 64bit kanálů (tři 128bit bloky), šest bloků L2 cache

a připojuje hub, který distribuuje data mezi méně náročné klienty

Další zajímavost pochází z úst Davea Baumanna (AMD) a týká se architektury. Zmínil, že každý ze tří 128bit bloků (z nichž se skládá 384bit paměťové rozhraní čipu Tahiti / Radeon HD 7900) je 2× větší než 128bit blok(y) řadiče čipu Pitcairn (Radeon HD 7800). Tato slova se dají vykládat dvě způsoby. (1) Baumann buďto pouze upozorňuje na fakt, že sběrnice Tahiti, která je stavěná na rychlé 6GHz+ GDDR5, vyžaduje pro stabilní běh výrazně víc tranzistorů než sběrnice GPU Pitcairn, která cílí na středně taktované ~5GHz GDDR5. (2) Nebo poukazuje na skutečnost, že v případě Tahiti, která byla prvním 28nm čipem - navíc podporujícím 6GHz+ paměti - věnovala AMD řadiči a rozhraní více tranzistorů, než bylo nezbytně potřeba. Prostě aby byla jistota, že rychlé paměťové rozhraní vyrobené na nevyzkoušeném procesu bude fungovat bez chyb.

Pokud bychom se drželi prvního výkladu, mohlo by to pro čip Hawaii znamenat, že 512bit ~5GHz rozhraní by dosahovalo nižších rozměrů než 384bit 6GHz+ rozhraní a bylo by výhodnější nejen z hlediska výrobních nákladů (menší čip), ale také z praktického hlediska (vyšší propustnost).

Ve druhém případě by to pro Hawaii znamenalo něco trochu jiného: Rozhraní by zůstalo 384bit, ale po zkušenostech s 28nm procesem by mohlo být lépe optimalizované a z plochy čipu by ukouslo výrazně méně než u Tahiti.

Kterou cestu AMD zvolila, si řekneme příští týden (případně můžete sami sledovat oficiální streaming na YouTube nebo webu AMD).