AMD sní o 10× rychlejším propojení čipletů, možná i o 6nm centrálním čipletu

„Například Ryzen 5000 využívá 2D pouzdření, ale přesto jde o stejný koncept, kde samozřejmě core complex využívá 7nm výrobu, ale I/O jádro 12nm… To funguje dobře do jisté úrovně, ale jakmile pro jednotlivé dílky potřebujete spojení o vysoké rychlosti, jde o úkol pro 3D technologii.“

Během tohoto vyjádření, které Rick Bergman poskytl pro The Street, byl zobrazen níže uvedený slajd s nápisem „>10× bandwidth density“ a rekapitulací různých typů spojení křemíku v rámci pouzdra za posledních pět let:

Slajd zjevně hovoří jak o procesorech, tak grafických čipech, takže ač citace začíná zmínkou o Ryzenech 5000, neznamená to, že se plánované desetinásobné zrychlení musí týkat zrovna samostatných procesorů. Ty to ani nepotřebují. Může se týkat grafických čipů, může se týkat čipletových APU. Může se týkat v podstatě čehokoli, co obsahuje GPU (protože ta mají požadavky na datovou propustnost přinejmenším o řád vyšší než CPU) a co je složeno z čipletů.

Což na druhou stranu - počínaje generací Zen 4 - mohou být i standardní procesory, neboť útržek z roadmapy AMD maluje generaci Raphael (Zen 4) možnost volitelného GPU Navi (asi 2). Tato možnost je značena přerušovaným orámováním, což znamená, že v době vzniku dokumentu ještě nepadlo definitivní rozhodnutí, ale s možností GPU pro standardní procesor se počítá (či počítalo).

Zatímco pro propojení procesorových a grafických čipletů by ale stačilo klasické propojení, které AMD používá u Zen 2 a Zen 3 (jádro integrované grafiky by prostě bylo na samostatném čipletu a nepotřebovalo spojení rychlejší než je PCIe), v případě velkého samostatného monolitického GPU, které chceme rozdělit na čiplety, taková možnost není. Datové přenosy, které se odehrávají na úrovni GPU, jsou řádově vyšší než datové přenosy odehrávající se na úrovni CPU, takže tam to bez >10× rychlejšího systému propojení nejde.

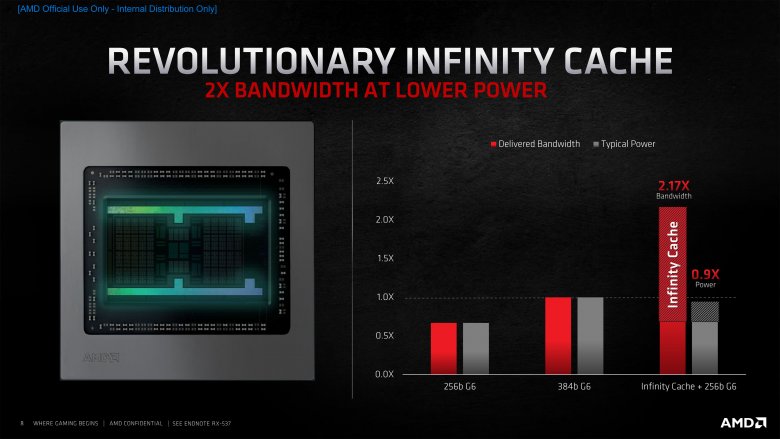

Slajd AMD navíc hovoří o hybridu 2,5D a 3D. Co to znamená: 3D je označení pro vrstvení čipů na sebe, příkladem může být Intel Lakefield. 2,5D naproti tomu spočívá v umístění spojovaných struktur vedle sebe s umístěním spojky (interposer nebo můstek) pod spojované struktury. Hybrid 2,5D a 3D bude patrně nějakým způsobem využívat kombinace obojího. Ilustračním příkladem (skutečně jde o příklad, nikoli tvrzení, že AMD něco takového chystá) by mohla být implementace Infinity Cache v rámci samostatné vrstvy na čipletu (3D), čímž by došlo ke snížení objemů přenosů mezi vedlejší strukturou (čiplet, paměť) propojenou přes interposer nebo můstek (2,5D).

Pokud je řeč o čipletech, nebude od věci zmínit i nejasnou situaci kolem centrálního čipletu Zen 4. Když v roce 2019 GlobalFoundries ohlásila tzv. 12nm+ proces, který by měl být dostupný v roce 2021, vypadalo to, že půjde o proces, kterým AMD bude vyrábět centrální čiplety nových generací procesorů. Dohoda o spolupráci definovaná v době, kdy se AMD a GlobalFoundries oddělily a aktualizovaná průběžnými dodatky, definuje, že AMD musí od GlobalFoundries odebírat dohodnuté objemy čipů až do roku 2024 a GlobalFoundries na oplátku musí poskytovat AMD výhodnější ceny. Centrální čiplety tak byly jediným rozumným kandidátem (snad vedle možnosti low-endových APU), kde by výroba u GlobalFoundries mohla mít smysl. Respektive se zdály být tím jediným, čím by AMD mohla smysluplně naplnit svoji část dohody.

V posledních měsících se ale odkudsi objevila zpráva (původ se mi nepodařilo dohledat), podle níž mají být centrální čiplety Zen 4 být vyrobeny 6nm procesem (patrně TSMC). 6nm proces TSMC je EUV proces, levnější varianta k 7nm EUV procesu. Těžko se však představují důvody, pro které by AMD měla tento proces preferovat před 12nm+ výrobou GlobalFoundries, s výjimkou nižší spotřeby. Centrální čiplet musí mít takový obvod, aby se na něj vešla všechna rozhraní (xGMI, PCIe, DDR, USB…) a zároveň zbytečně nezvyšovat cenu. 6nm proces by plochu a tudíž i obvod centrálního čipletu (IOD) výrazně zmenšil, takže těžko říct, zda by mohl tyto požadavky naplnit. Smysl by mohl mít, pokud by měl integrovat nějakou funkcionalitu navíc (například integrované GPU pro Raphael?). Pak by mohlo mít v desktopu smysl 6nm IOD od TSMC a v serverech a pracovních stanicích 12nm+ IOD od GlobalFoundries.

Každopádně se zdá, že ať už integrace GPU do klasických procesorů nebo rozložení samostatných GPU na čiplety podmiňuje AMD přítomností Infinity Cache, která snižuje objemy datových přenosů a tím pádem o něco usnadňuje implementaci takového řešení.

The Street aj.