Oficiálně: Hynix bude do základen HBM4E integrovat logiku, cache a síťovou paměť

Pokud jste četli náš květnový článek, mohli jste krom samotné informace o 5nm a 12nm výrobě zaregistrovat i náš odhad, k čemu by nasazení těchto výrobních procesů v kontextu HBM pamětí mohlo být dobré.

Tyto předpoklady nyní oficiálně potvrdil Hynix, který nastínil plány s HBM4 a HBM4E. První zmíněná generace přesune řadič HBM na úroveň křemíkové základny, od čehož si výrobce slibuje navýšení energetické efektivity a možnost zvýšení přenosové rychlosti.

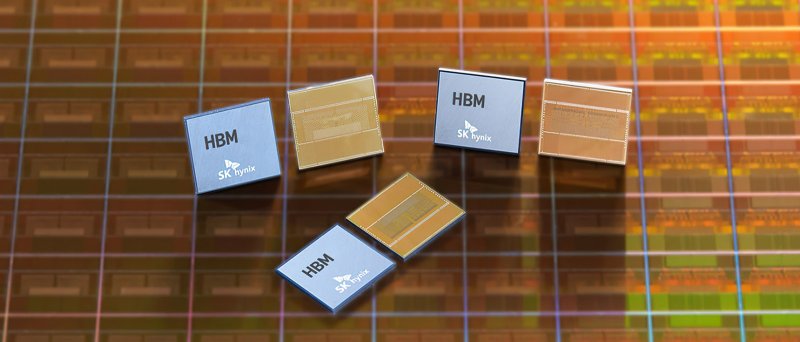

Hynix (Shutterstock)

S HBM4E má ještě ambicióznější plány; jejich základnu plánuje vybavit vlastní cache, dále doplněním výpočetních obvodů (logiky) a případně i síťovou pamětí. Zde již Hynix podrobnosti neuvádí. Lze však odvodit, že výpočetními obvody je míněna technologie PIM (Processing In Memory), která umožňuje provádět jednoduché operace s daty na úrovni HBM modulu bez potřeby přesunu dat na úroveň hlavního čipu (např. akcelerátoru, GPU ap.), což šetří energii a výpočetní čas. Cache může zkracovat latence, pravděpodobně však ne navyšovat přenosovou rychlost, neboť rychlost HBM paměti a rychlost HBM rozhraní, které modul spojuje s hlavním čipem, je obvykle totožná (z cache by v takovém případě nebylo možné data přesouvat rychleji než přímo z paměti).

HBM4 a samozřejmě i HBM4E jsou zatím poněkud vzdálené standardy, alespoň co do nasazení těchto pamětí do hardwaru dostupného na trhu. Vývoj HBM4 začne u Hynixu v roce 2025, vývoj HBM4E o rok později. Společnost se na tento počin připravuje již od loňského roku, kdy začala nabírat inženýry se zkušenostmi s vývojem CPU a GPU, aby si zajistila potřebné IP. Na přelomu roku 2023 / 2024 pak společnost přijala několik zaměstnanců pocházejících z Intelu.

Zatím není známo, zda chce Hynix tyto (řekněme) změny prosadit do budoucích standardů HBM, nebo o to naopak zájem nemá a rád by je nabízel exkluzivně jako úpravy na míru.