Paměťová architektura, GDDR5

Kapitoly článků

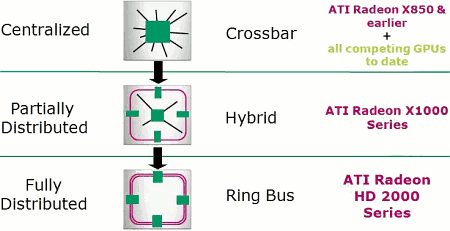

Na úvod si připomeňme evoluci vývoje paměťového řadiče u ATI/AMD.

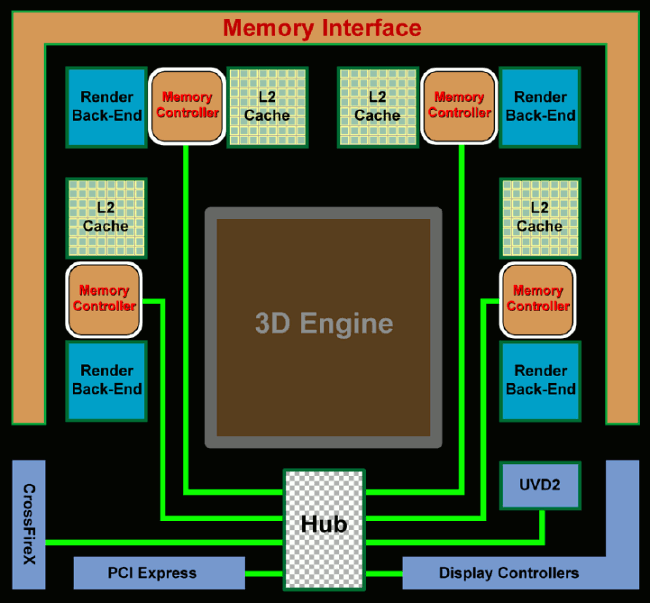

Současná generace byla ve vývoji na poměrně flexibilním bodě prstencové sbernice, Radeony HD 4800 jdou ještě dále. Na svět přchází distribuovaný design řadiče využívající centrální hub. Kdo z vás se trochu vrtá v sítích (nebo hrál Falouta 1 :-), už ví, která bije.

Jednotlivé řadiče jsou „rozesety“ po obvodu čipu (viz schéma GPU v úvodu článku) a napojeny na části s největší (s)potřebou paměťové propustnosti. Využití této „dlaždicové“ metody rozdělení sběrnice a současně užší (ale superrychlé) 256bitové šířky ve výsledku snižuje latence při přenosu dat, rozměry GPU a ve výsledku i spotřebu čipu.

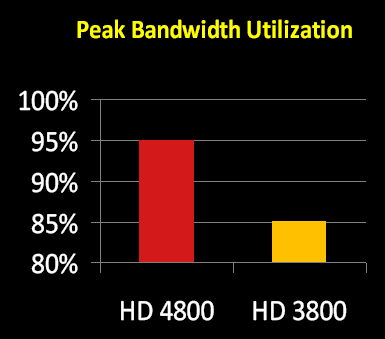

Centrální hub pak pracuje jen s minimální částí celkové propustnosti, ve výsledku tak AMD u RV770 oproti RV670 zvýšila efektivní využitelnou paměťovou propustnost na 95 %.

Geometry shader, tesselace

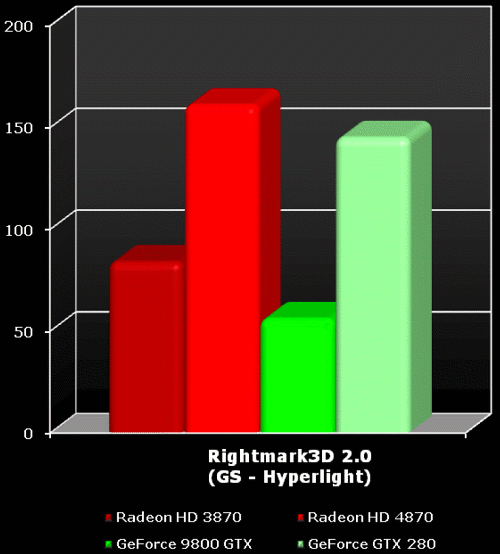

RV770 podporuje 4× více geometry shader výpočetních vláken. Současně umí podržet těmito shadery vygenerovaná data v sobě, což zrychluje další výpočty. Tesselační jednotka dostala do vínku podporu instancingu a je nyní kompatibilní s DirectX 10.0 i 10.1.

GDDR5

Krátkou pasáž věnujem i GDDR5 pamětem a důvodům, proč si je AMD vybralo pro Radeon HD 4870. V krátkosti souhrn nevýhod GDDR3 pro použití s malým 55nm GPU dle Joea Marciho, šéfa ASIC Engineering skupiny v AMD:

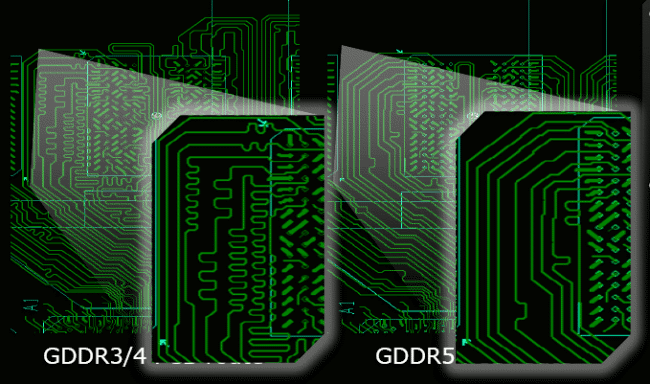

- GDDR3 čipy jsou VELKÉ

- Pouzdra jsou VELKÁ

- Karta je VELKÁ

- Spotřeba je VELKÁ

- VELKÉ je ŠPATNÉ

Nu dobrá, je to sice jak pro retardované chovance, ale poselství je jasné. GDDR3 už se do budoucna AMD nehodí do krámu a jistě i proto, že Qimonda přeskočila GDDR4 a i další výrobci již mají GDDR5 čipy dávno venku, volí AMD opět tradiční cestu a to použití toho nejnovějšího dostupného pro své vyšší modely grafik.

Vše je v rámci příprav pro budoucí 40nm GPU, pro něž aktuálně na trhu neexistuje přijatelné řešení. Pro budoucí generace AMD chce dvakrát až třikrát výkonnější paměti než jsou nyní GDDR3, ale zpětně kompatibilní a takové, jejichž spotřeba s propustností neporoste (no to jsme zvědavi).

AMD se ve věci kolem GDDR5 v minulosti i současnosti hodně snažila v organizaci JEDEC a na využití 512Mbitových a 1Gbitových čipů již delší dobu spolupracuje s firmami Qimonda, Hynix a Samsung, tedy třemi klíčovými hráči na tomto poli.

Momentálně tedy mohou výhledově hovořit o 3,2 až 7,0GHz čipech o velikosti 512 MB a 1 a 2 GB s propustností 12,8 až 28,0 Gbit/s na čip (což při osmi kouscích slibuje až 224 GB/s!). S napájením 1,5 V přitom takový čip při 5,0 GHz spotřebovává pouze 2,5 W (tedy 20 W při osmi čipech na kartě).

Mezi novinkami proti GDDR4 je protokol realtime detekce chyb v obou směrech (čtení-zápis), nikoli dual data-rate, ale quad data-rate, dále řada vylepšení v logice čtení/zápisu, interní/externí VREF, nový Data Mask algoritmus, techniky pro snižování spotřeby a ×16 režim.

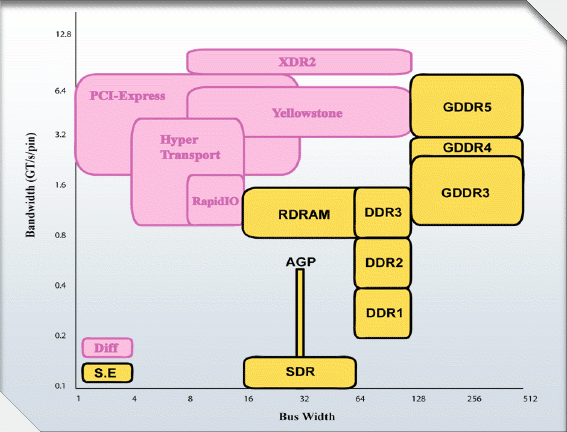

Další osvědčenou zajímavostí však je Single Ended Signaling. Často používané diferenční signálování (rozdíl dvou stavů) spotřebovává více napájení a vyžaduje dvojnásobný počet pinů. Naproti tomu Single Ended signálování tyto nevýhody smazává (a že jej grafikcé paměti používají již pěkně dlouho).

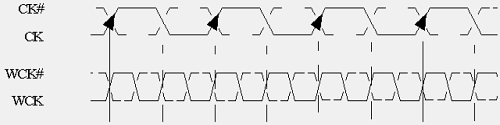

Metoda taktování čipů je zpětně kompatibilní. Tradiční CK takty se používají pro přikazy/adresy, kontinuálně s nimi však beží WCK takty, rozhraní je pak asymetrické, časování čtení a zápisu se provádí v GPU a výsledkem je škálovatelný výkon.

S GDDR5 současně přijde na svět několik technik pro stabilní přetaktování. V pouzdře obsažené termosenzory budou schopny řídit změny časování pamětí za běhu, aby tak zůstaly stabilní i při přetaktování (prostě thermal-throttling, jak jej známe už od prvních Pentií 4 :-).

Pátá generace GDDR také přináší čistší návrh PCB, kde se počítá s kratšími trasami datových vodičů za současně zlepšené jejich izolace. Ono je to při těch vysokých frekvencích celkem logické.