Přelomové FinFLEX od TSMC: Tři způsoby optimalizace tranzistorů v jediném čipu

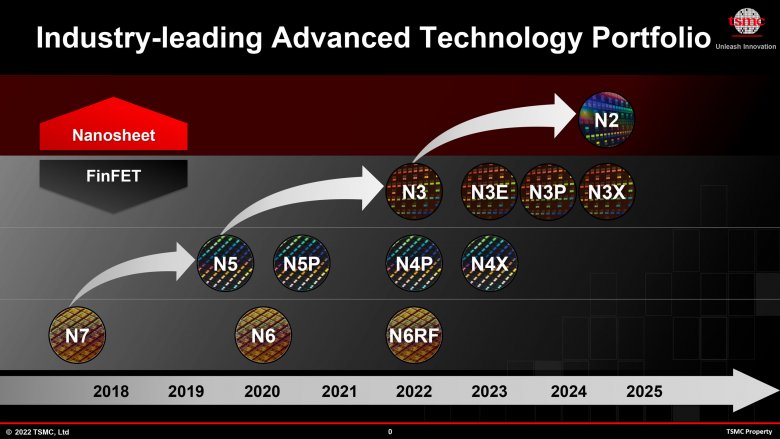

Prakticky každý proces TSMC vzniká v několika variantách. U 3nm jsme slyšeli o základní verzi N3 určené primárně pro ultramobilní ARM SoC, o výkonnější N3P, o tajemné N3B a dále jsou v přípravě N3E a N3X. Dnes bude řeč o N3E, neboť práv s tou představila TSMC technologii FinFLEX. Její podstatou jsou tři různé konfigurace tranzistorů, které jsou optimalizované pro různá cílová nasazení.

- N3E 2-1 Fin - podobná jako základní N3, dosahuje vysoké denzity a nízké spotřeby, ale i výkonu

- N3E 3-2 Fin - proti 4 nm prakticky nezmenšuje čip a spotřebu, ale výkon je o třetinu vyšší

- N3E 2-2 Fin - kompromis mezi oběma

Podrobnější (číselná) srovnání oproti 5nm procesu najdete v tabulce níže (vyžluceno):

| TSMC | |||

| proces | denzita | výkon | spotřeba |

|---|---|---|---|

| 7nm (N7) | +59 % vs N10 | ? | -40 % vs. N10 |

| 7nm (N7P) | ? | +7 % vs. N7 | -10 % vs. N7 |

| 7nm+ (EUV / N7+) | +20 % vs. N7 | +10 % vs. N7 | -15 % vs. N7 |

| 6nm (N6) | +18 % vs. N7 | ? | ? |

| 5nm (N5) | +80 % vs. N7 | +15 % vs. N7 | -30 % vs. N7 |

| 5nm (N5P) | ? | +7 5 % vs. N5 | -10 % vs. N5 |

| 4nm (N4) | +6 % vs. N5 | téměř beze změny | beze změny |

| 4nm (N4P) | +6 % vs. N5 | +11 % vs. N5 +6 % vs. N4 | -22 % vs. N5 |

| 4nm (N4X) | ? | +15 % vs. N5 @1,2V +4 % vs. N4P @1,2V | ? |

| 3nm (N3) | +70 % vs. N5 3× vs. N7 | +10-15 % vs. N5 +32 % vs. N7 | -25-30 % vs. N5 -51 % vs. N7 |

| 3nm (N3B) | ? | ? | ? |

| 3nm (N3E 3-2 Fin) 3nm (N3E 2-2 Fin) 3nm (N3E 2-1 Fin) | +18 % vs. N5 +39 % vs. N5 +56 % vs. N5 | +33 % vs. N5 +23 % vs. N5 +11 % vs. N5 | -12 % vs. N5 -22 % vs. N5 -30 % vs. N5 |

| 3nm (N3P) | ? | ? | ? |

| 3nm (N3X) | ? | ? | ? |

| 2nm (N2) | +70% vs. N3? | ? | ? |

N3E 3-2 Fin vypadá na první pohled skvěle z hlediska x86 procesorů Jenže je tu problém: Skoro nesnižuje ploch (nezvyšuje denzitu). Každá další generace procesu mívá cenu za wafer o 50-80 % vyšší než předchozí. Pokud tedy z waferu N3E 3-2 Fin vypadne cca o 15 % více o 33 % rychlejších procesorů než z waferu N5 a cena za wafer bude o 70 % vyšší, bude mít čip o 10 % horší poměr cena / výkon než jeho 5nm předchůdce. To by moc ekonomicky nefungovalo (většinou zákazníci očekávají, že s novou generací dostanou za stejné peníze vyšší výkon než u generace předchozí).

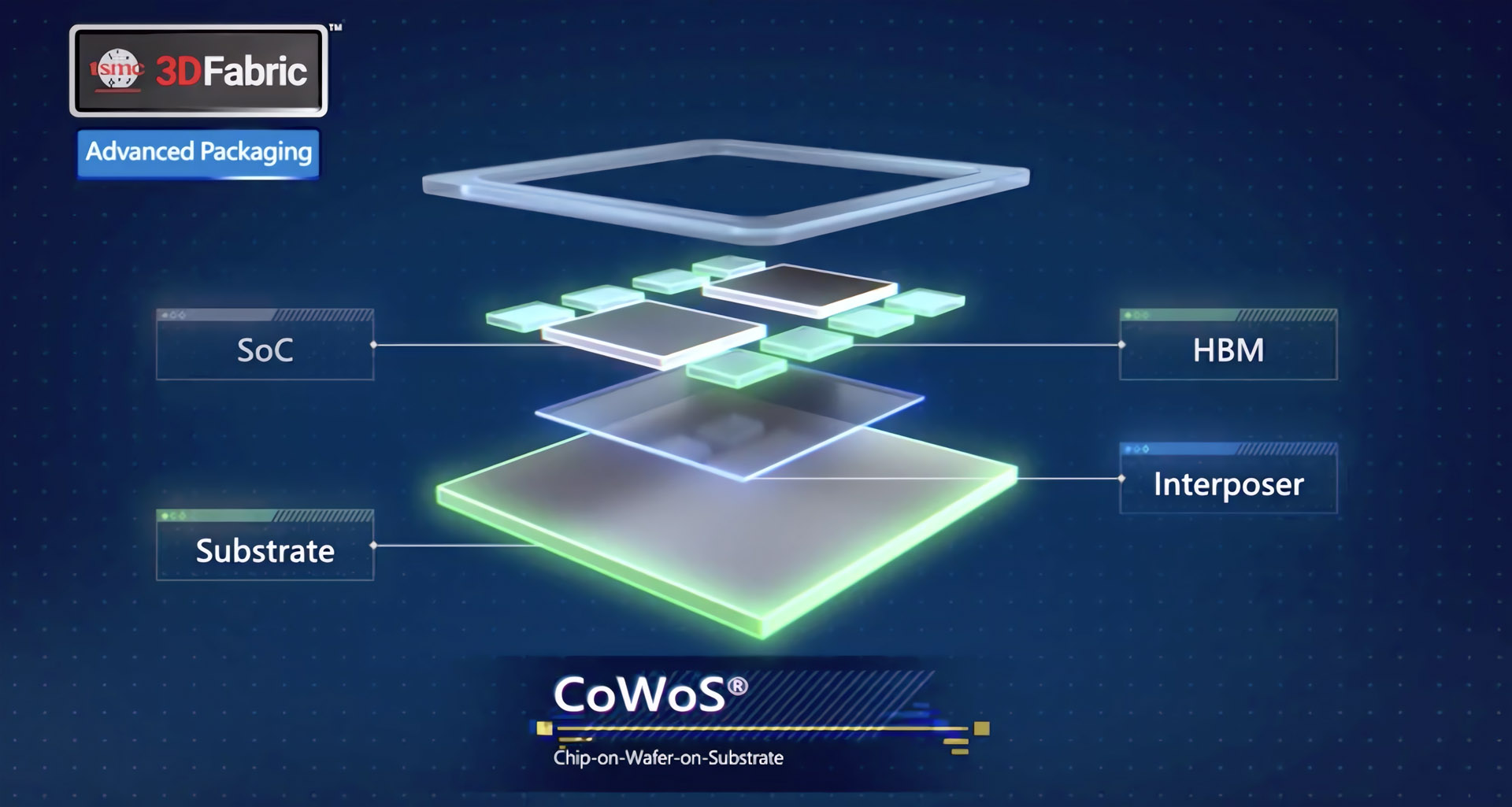

I na to zjevně TSMC myslela, protože umožňuje kombinovat jednotlivé varianty N3E procesu v rámci jednoho čipu. Kupříkladu u ARM SoC se třetmi typy jader je možné nejvýkonnější vyrobit na N3E 3-2 Fin, střední na N3E 2-2 Fin a malá úsporná na N3E 2-1 Fin. Kupříkladu u APU pak může být nejvýkonnější varianta použitá pro x86 jádra, střední pro grafiku úsporná pro ostatní obvody.

V čem spočívá ta výhoda? Že negativum v podobně snížené denzity (vyšších nároků na plochu) se může týkat pouze samotných procesorových jader, která obvykle tvoří jen malou část plochy (např. u APU Rembrandt odhadem pod 10 %).

Proces N3E s FinFLEX by měl být podle TSMC dostupný již v příštím roce, takže bude prvním nástupcem základního N3 procesu. Do poloviny roku 2024 dorazí proces N3P optimalizovaný pro vyšší výkon a někdy na přelomu roku 2024 / 2025 dorazí N3X, od něhož lze očekávat výkon na úrovni chystaného 2nm procesu, ovšem při podstatně nižší denzitě a vyšších energetických nárocích. Mohl by se stát podobnou alternativou k 2nm výrobě jakou bude N4X k 3nm výrobě.

TZ TSMC