TSMC zahájí masovou výrobu na 5nm procesu již v březnu

TSMC, která dříve v letošním roce avizovala zahájení experimentální výroby na 5nm procesu v dubnu letošního roku a spuštění velkokapacitní sériové výroby v prvním pololetí 2020, má podle zdrojů redakce webu DigiTimes s přípravami náskok. Vše jde zřejmě velmi dobře, takže se ve velkém na pěti nanometrech nezačne vyrábět na konci avizovaného období, ale o tři měsíce dříve, v březnu 2020. Mimochodem přesně o rok dříve se spustila 7nm EUV výroba.

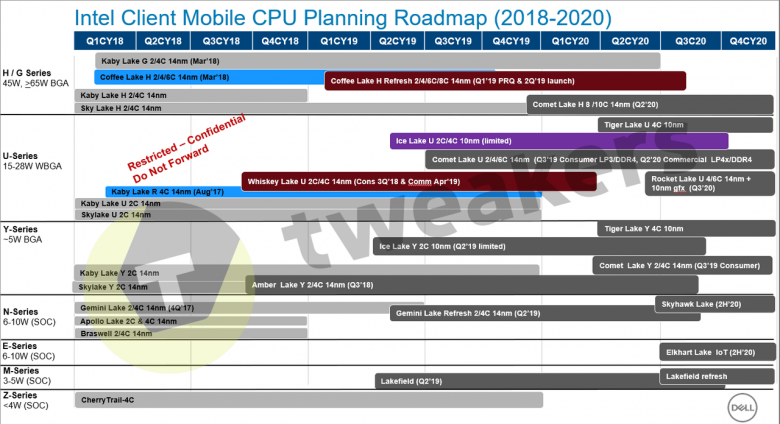

Na počátku roku 2020 je zajímavá jedna věc. Intel sice formálně zahájil 10nm výrobu již před poměrně dlouhou dobou, ale zároveň tehdy přiznal, že nejde o sériovou výrobu a 10nm procesory Canon Lake byly de facto vzorky, aby dodržel slib s vydáním této generace. Přestože má na letošní předvánoční trhy dodávat notebooky s 10nm procesory Ice Lake, v roadmapě má Intel uvedeno, že jde o limitované dodávky…

…takže stále nelze hovořit o velkoobjemové výrobě. 10nm produkty, o kterých by bylo možné hovořit jako o velkoobjemově vyráběných, jsou podle této roadmapy chystané na přelom prvního a druhého kvartálu 2020. Tedy na dobu, kdy má TSMC rozběhnout 5nm výrobu. Protože mezi klíčovými generacemi výrobních procesů bývají prodlevy 2-3 roky a v tomto případě půjde o rozdíl dvou generací, nezdá se být loňský odhad analytiků z Rosenblatt Securities zdaleka tak nadsazený, jak se mohl jevit loni.

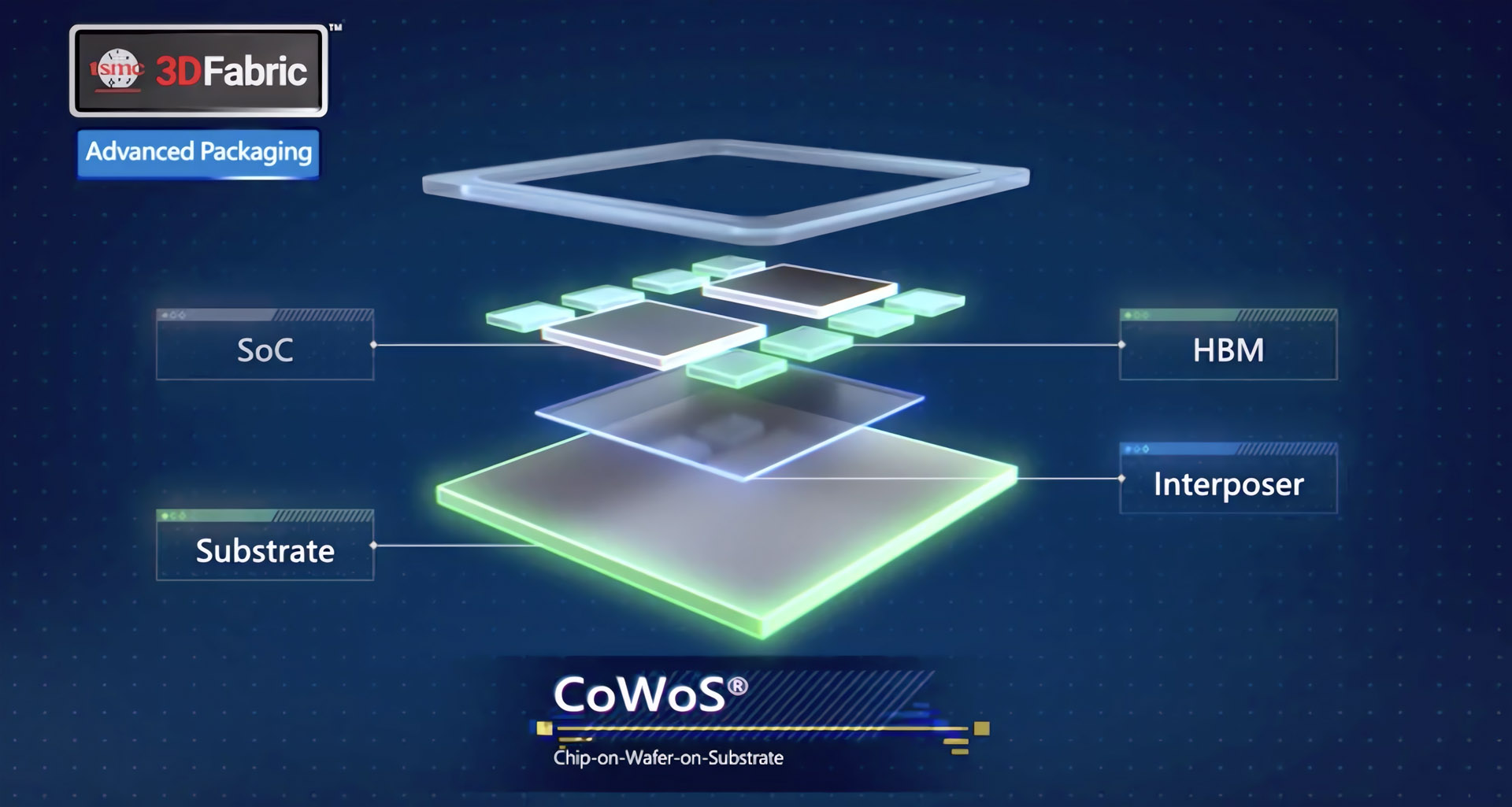

Na druhou stranu je potřeba říct, že ač 5nm proces TSMC významným způsobem zmenší plochu čipu (denzita je o 80 % vyšší, takže 5nm čip může být při stejné ploše se 7nm čipem vybaven 1,8× vyšším počtem tranzistorů), spotřeba klesá pouze o 30 %. Důležité pak je, že pokles spotřeby se vždy uvádí pro stejný návrh čipu běžící na stejných taktech. Jinými slovy, pokud by šlo o náš hypotetický návrh s 1,8× vyšším počtem tranzistorů, můžeme vypočítat, že i při snížení spotřeby o 30 % bude celková spotřeba 5nm čipu o konkrétní ploše 1,26× vyšší než spotřeba 7nm čipu o stejné ploše a stejných taktech (a stejné architektuře).

U produktů, které jsou omezeny spotřebou, tedy nebude snadné potenciál o 80 % vyšší denzity využít. Buďto jej půjde využít jen částečně (aby byla zachovaná spotřeba), nebo bude muset být vyšší spotřeba kompenzována nižšími takty (což není zrovna oblíbené), nebo bude muset být kompenzována energeticky efektivnější architekturou (což stojí tranzistory navíc, takže hlavní výhoda proceu částečně padne na kompenzaci hlavní nevýhody procesu).