Zen 5 APU / Strix Point může nést L4 cache

Čímž nám zároveň zapadá do (již) seriálu o vývoji cache u připravovaných generací procesorů a APU:

- AMD chystá revoluci v cache: SLC, jednotná L2, L3 přesunutá do V-cache

- Co je SLC a jaký má význam ve světě x86 desktopu

- AMD se Zen 5 poprvé za 12 let zvýší kapacitu L1 cache nad 32 kB

Jak již bylo řečeno, velké procesory postavené na architektuře Zen 5 vzniknou pravděpodobně na bázi čipletů o 16 jádrech. Aby se do čipletů (bez výrazného navýšení plochy křemíku) dvojnásobek jader vešel, vypadne L3 cache, která se přesune na úroveň V-cache. Kolik přesně jí bude, zatím není známo. Pokud by zůstala v permanenci stávající 7nm 36mm² 64MB V-cache, pak by u Zen 5 zůstal zachován poměr 4 MB L3 cache na jádro, ovšem z důvodu 64MB monolitických bloků by byla efektivněji využitelná u aplikací, pro které je kapacitně limitující stávající monolitická 16MB cache (integrovaná přímo v čipletu). Teoreticky by připadal v úvahu i možnost vzniku 128MB V-cache, která by se se 72mm² mohla na čiplet vejít a dát vznik nástupci Epycu Bergamo. To už je ale jen spekulace vycházejí z možností technologie.

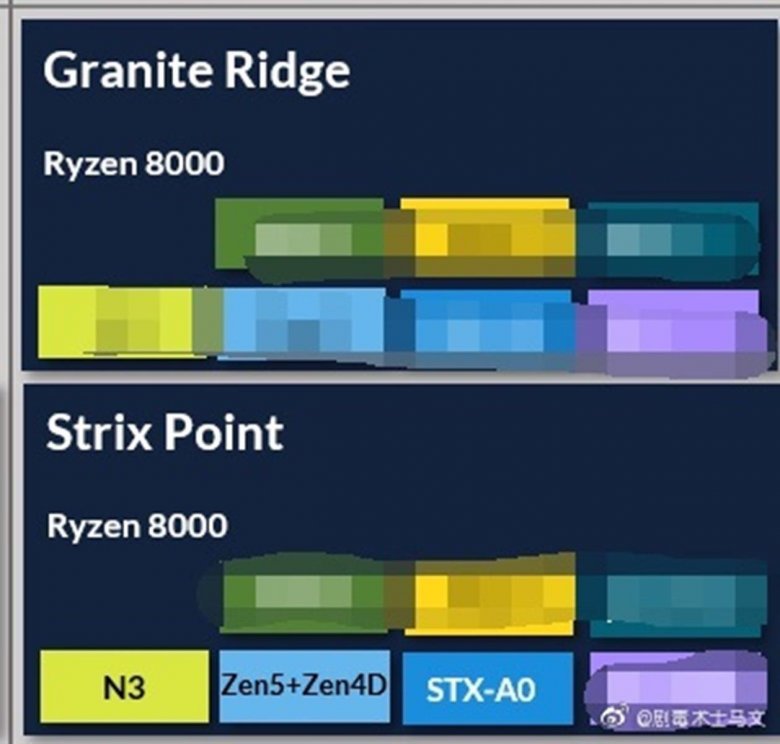

U APU, kde je podstatnou částí procesoru integrovaná grafika, bude situace jiná. APU Strix Point má krom jader Zen 5 obsahovat i upravená jádra Zen 4. Nevíme zatím, kolik jich bude (ani jedněch, ani druhý, ani celkem). Konkrétní hodnota bude úzce souviset s faktem, kde udělá AMD dělící čáru v mobilním segmentu. Například s generací Zen 4 budou APU pokrývat už pouze segment do ~35 W včetně, čemuž bude odpovídat maximálně 8 jader, přičemž ~45 wattů a výš již bude doménou velkých čipletových procesorů (které najdou díky malé integrované grafice uplatnění i v noteboocích), takže přinesou do notebooků 12 až 16 jader Zen 4.

výřez ze starší roadmapy AMD

Je známo, že Zen 5 přinese 16jádrové čiplety. Nevíme však, zda AMD zvýší dělící hranici mezi APU a velkými procesory, tedy zda APU zůstanou osmijádrová a vše vyšší budou pokrývat čipletová řešení, nebo zda se i hranice pro APU zvýší třeba na 12 nebo 16 jader. Nutné to není, pokud Zen 4 přinese do notebooků až 16 velkých jader, tak nebude vysloveně nutné, aby hned další generace v podobě Zen 5 přinesla 32jádrové notebooky a APU se adekvátně tomu posunula na až 16 jader. Vyloučit však nelze žádnou možnost.

Víme však, že u APU bude oproti velkým procesorů odlišná struktura cache, což bude souviset s přítomností integrované grafiky. Začněme ale od procesorových jader. Ta (není jisté, zda se to týká jen upraveného Zenu 4 nebo všech procesorových jader včetně Zen 5) budou mít zvětšenou L2 cache a naopak zmenšenou L3 cache. Zde lze hledat určitou spojitost s informací, že Zen 5 přinese sjednocenou L2 cache, kdy jeden velký blok bude obsluhovat všechna jádra (oproti současnému stavu, kdy každé jádro má svůj malý blok L2). Sjednocený blok L2 by tak čistě teoreticky mohl sloužit jak jádrům Zen 5, tak Zen 4, což by vysvětlovalo onu vysokou kapacitu L2. Následovat má nepříliš velká L3 cache. Řekněme, že pokud by L2 byla 16MB, pak by asi i L3 mohla dosahovat této kapacity.

K tomu může být Strix Point vybaven L4 cache. Leaker Greymon55 tuto informaci považuje za jistou (věrohodnou) a RedGamingTech připouští, že by její přítomnost mohla být volitelná. Oba zdroje předpokládají, že by mohlo jít o V-cache (byť explicitně to potvrzeno není). Tato L4 cache by fakticky mohla být onou opakovaně zmiňovanou SLC, tedy pamětí sloužící potřebám procesorových i grafických jader. Možností, jak by mohla být implementována, je celá řada - hypoteticky od 7nm 64MB konfigurace známé z Ryzen 7 5800X3D přes 6nm řešení použité na Navi 31 / 32 až po nějakou jinou variantu navrženou na míru pro daný produkt (i 32MB kapacita by grafickému jádra velmi podstatně prospěla a nejspíš i stačila).

Stávající (7nm 64MB) V-cache na čipletu Zen 3; zdroj: AMD

Pokud bychom se pustili na tenčí led spekulací, pak přítomnost (byť menší) L3 cache indikuje, že by APU skutečně mohlo být schopno velmi obstojně fungovat i bez SLC / L4. Přítomnost SLC / L4 by pak mohla být doménou „high-endových“ modelů. Jak konkrétně výkonných, je otázka. Nyní má AMD v mobilním segmentu 6nm APU Rembrandt se 768 stream-procesory architektury RDNA 2, jejíž snížené nároky na datovou propustnost v kombinaci s pamětmi DDR5 mají za následek, že toto řešení žádnou velkou cache nevyžaduje. Příští generace, 5nm APU Phoenix s jádry Zen 4, přinese minimálně 1024 stream-procesorů RDNA 2, možná i více (1152?). S ohledem na zrychlování DDR5 by si i takové řešení mohlo vystačit bez velké cache (i když některé starší zdroje možnost Infinity Cache nebo SLC v kontextu Phoenix zmiňovaly). APU Strix Point se prozatím tváří jako 3nm produkt (velké procesory, které vyjdou dřív, se pravděpodobně přesunuly na 4nm proces) a jako takový by mohlo nabídnout prostor pro výrazné povýšení integrovaného jádra jak co do počtu stream-procesorů, tak co do použité architektury (RDNA 3). Lze si proto představit přítomnost až 2048 stream-procesorů RDNA 3, které by mohly být v této plné konfiguraci doplněny větší cache (SLC). Ořezané modely (s třeba 1280-1536 stream-procesory) by si pak vystačily čistě s dostupnými (LP)DDR5(X), bez velké cache.

Vydání velkých procesorů Zen 5 / Granite Ridge pro desktop se očekává na konci roku 2023. APU Strix Point (Zen 5 + Zen 4 + RDNA 3) by mohlo následovat v lednu na CES 2024 (pro notebooky). Půjde o konkurenci první generace čipletových procesorů Intel Meteor Lake (druhé pololetí 2023?) a snad i jejich nástupce Arrow Lake (2024).

ilustrace: John Booth, Greymon55, RGT