AMD se Zen 5 poprvé za 12 let zvýší kapacitu L1 cache nad 32 kB

Minulý týden jsme si popsali, že podle dostupných informací plánuje AMD se Zen 5 unifikovat L2 cache (tzn. že namísto sady samostatných cache pro každé jádro bude k dispozici jedna velká společná) a dále, že L3 cache se pravděpodobně přesune mimo procesorový čiplet, pravděpodobně na úroveň V-cache.

- AMD chystá revoluci v cache: SLC, jednotná L2, L3 přesunutá do V-cache

- Co je SLC a jaký má význam ve světě x86 desktopu

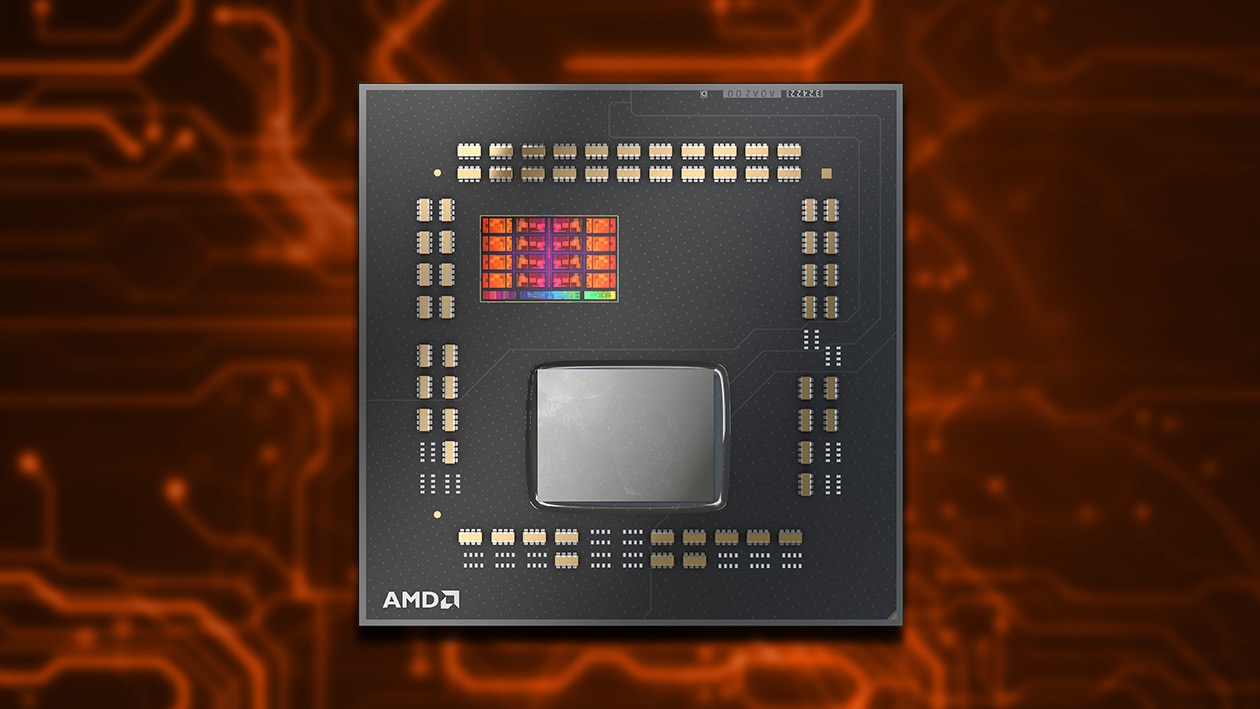

Co k druhému popsanému kroku AMD vede, je docela zjevné při pohledu na snímek procesorového čipletu Zen 3:

Modro-oranžovo-žluté bloky jsou procesorová jádra s L2 cache. Celá fialovo-červeno-růžová část je L3 cache. Na první pohled je patrné, že kdyby v čipletu L3 být nemusela, vešlo by se do něj 2× více procesorových jader. Voilà - ona v něm L3 být nemusí, díky možnosti jejího přesunu do V-cache. Přesun L3 na úroveň V-cache jde tak ruku v ruce zdvojnásobení počtu jader na čiplet.

Právě to se stane standardem u velkých procesorů postavených na architektuře Zen 5: Epyc, Threadripper i Ryzen (AM5 a velké notebooky). Čím dál více se jeví jako pravděpodobné, že kombinace jader Zen 5 a Zen 4 zůstane doménou APU (Strix Point), zatímco čipletová řešení budou postavena čistě na Zen 5.

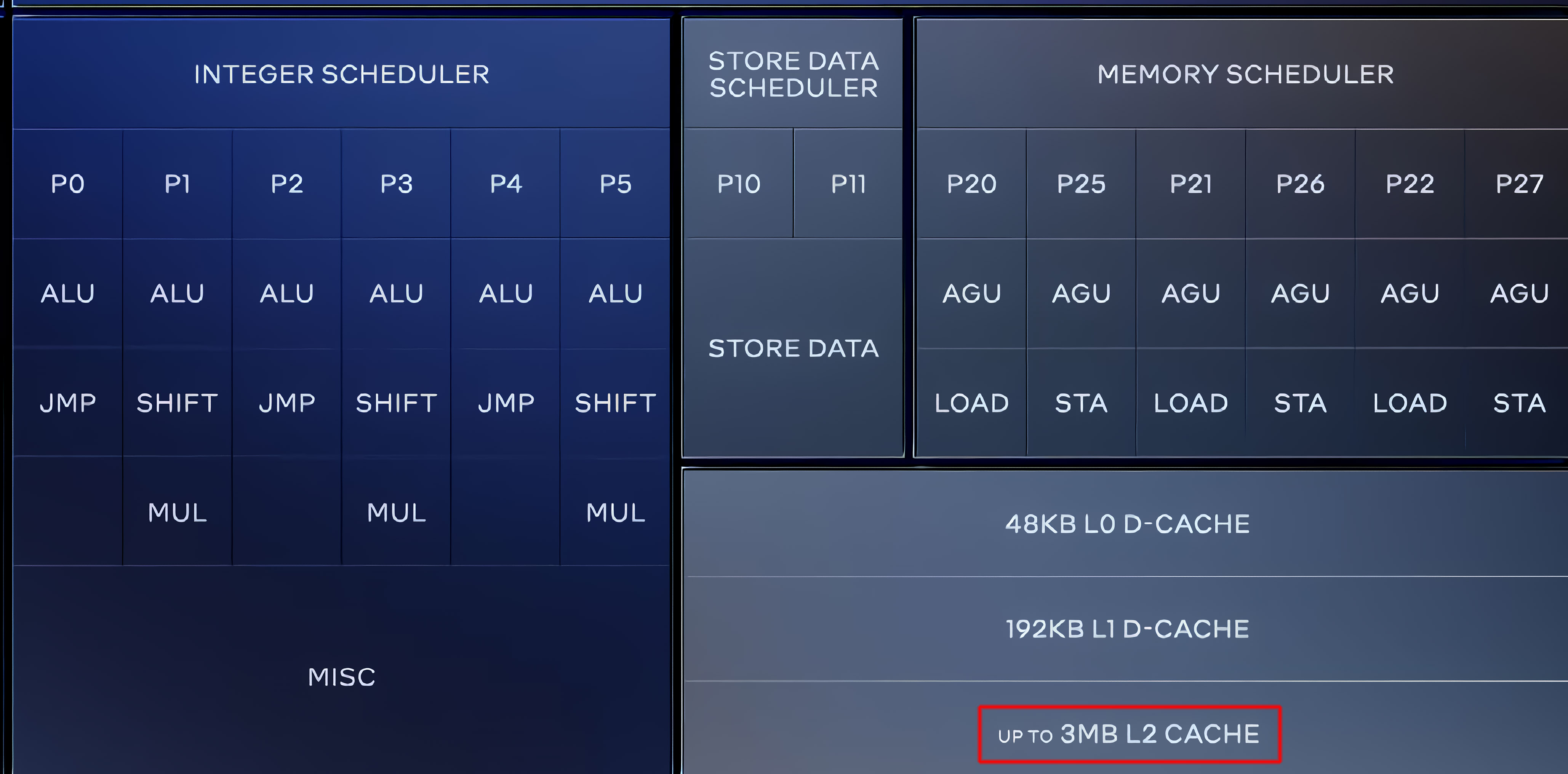

O Zen 5 se proslýchá, že přinese významné navýšení IPC (možná až kolem 30 %), ovšem nezdá se, že by přinesl významné navýšení taktů (vypadá to zhruba na 200 MHz). To docela koresponduje s další informací, kterou se o systému cache této generace dozvídáme: AMD po velmi dlouhé době navýší kapacitu L1 cache. Není specifikováno přesně o kolik ani zda se změna dotkne datové cache, instrukční cache nebo obou, ale navýšení má být „významné“. Současné generace jsou vybavené 32 kB datové L1 cache na jádro a bylo tomu tak od nástupu Zenu. Stavební stroje přišly s 16 kB (Bulldozer, Piledriver, Steamroller) a ke konci jejich éry došlo k navýšení na 32 kB (Excavator). Celá éra Athlonů (ať už slotových, socket A nebo následujících 64 bit řad K8 a K10) byla vybavena 64 kB a celá éra jejich předchůdců K6 nesla 32 kB.

Čistě empiricky můžeme z těchto hodnot vypozorovat, že jádra dosahující maximálních taktovacích frekvencí byla vybavena nízkou kapacitou L1 cache (16 kB), jádra dosahující na svou dobu středně vysokých taktovacích frekvencí nesla 32 kB L1 cache a jádra dosahující spíše nižších taktů nesla 64 kB.

| cache | L1 | L2 | L3 | ||||

|---|---|---|---|---|---|---|---|

| data | inst. | TLB | na jádro | TLB | na jádro | konf. | |

| Zen | 32 kB (4-way) | 64 kB | 512e | 512 kB | 1536e | 2 MB | [8]+[8] |

| Zen 2 | 32 kB (8-way) | 32 kB | 512e | 512 kB | 2048e | 4 MB | [16]+[16] |

| Zen 3 | 32 kB (8-way) | 32 kB | 1024e | 512 kB | 2048e | 4 MB | [32] |

| Zen 3 + V-cache | 32 kB (8-way) | 32 kB | 1024e | 512 kB | 2048e | 12 MB | [32+64V] |

| Zen 4 | 32 kB (8-way) | 32 kB | ? | 1024 kB | ? | 4 MB | [32] |

| Zen 5 | 64 kB? | ? | ? | 1024 kB | ? | 4 MB? | [64V]? |

Pokud dojde k významnému navýšení kapacity L1 cache (64 kB na jádro?), nebude divu, pokud se taktovací frekvence navzdory nástupu nového procesu příliš neposunou. Kromě jiného zatím není jasné, zda AMD u čipletového řešení nasadí 3nm nebo 4nm proces TSMC. Mezi různými zdroji jsou trochu rozpory, ale vypadá to, že 4nm proces na generaci Zen 5 nasazen bude a 3nm sice AMD využije rovněž, ale nejspíš na nějaké vybrané nebo později vydané produkty (APU? refresh?).

Zvětšení CCX znamená, že při 16 jádrech a 1 MB L2 cache pro každé ponese celý CCX velkou 16MB L2 cache, která tak prakticky bude dosahovat kapacity L3 cache původního Zenu, ale bude rychlejší a efektivnější (funkčně monolitická, nikoli rozdělená na oddíly).

L3 cache, která se pravděpodobně dostane na úroveň V-cache, by čistě teoreticky mohla být 64MB. Podle dostupných informací má totiž být vyráběna na starším (cenově příznivějším) procesu, než samotný procesorový čiplet. Připomeňme dvě důležitá fakta:

- Nové procesy zmenšují logiku, ale na plochu cache (SRAM) příliš nesnižují. Vzhledem ke strmému růstu cen nových procesů tedy není ekonomicky zajímavé převádět čipy obsahující velké množství SRAM na nové výrobní technologie (cena vzroste, plocha moc neklesne). To může být pro AMD druhým zásadním důvodem, proč cache přesouvá na samostatně vyráběný křemík. Získá tím oddělení čipletu s převahou logiky, pro který se vyplatí nasazení nových procesů a čiplet s převahou SRAM, pro který se vyplatí využití starších generací. Z toho dále vyplývá jistá diverzifikace výrobních procesů a tím efektivní zvětšení výrobních kapacit (než kdyby vše vznikalo na jednom procesu).

- TSMC s možnost vrstvení přišla se 7nm procesem. Její technologie neumožňovaly pro účely vrstvení kombinovat 7nm proces s jakýmkoli starším. Z výše řečeného vyplývá, že na novější procesy (5nm-4nm-3nm) však nejspíš bude možné navrstvit křemík vyráběný starším (7nm nebo 6nm) procesem. Pokud by V-cache nadále vyráběla na 7nm lince, pak by při 64 MB kapacitě zůstaly zachovány stávající rozměry. Na Zen 5 čiplet by se tak vešlo 64 MB L3 cache s tím, že procesorová jádra umístěná po obvodu čipletu by (podobně jako nyní) nebyla překryta V-cache, ale jen „výplní“. 64 MB L3 by byla i vcelku rozumná hodnota pro 16 jader. Kapacita na jádro by zůstala stejná jako u klasických Zen 3 a Zen 4, ale vznikem monolitické 64 MB L3 cache by toto řešení bylo efektivnější.

Uvědomíme-li si, jak razantní změny AMD chystá s generací Zen 5, aby dosáhla ~30% nárůstu IPC při snaze o udržení výrobních nákladů na přijatelné úrovni, jen těžko si představit, že by je mohla s každou další generací opakovat, natož překonávat. Bude velmi zajímavé, kam se procesorový výkon dostane se Zen 7 (Zen 6 bude evolucí Zen 5 jako je Zen 4 evolucí Zen 3 nebo Zen 2 evolucí Zen).

Desktopové procesory na bázi jader Zen 5 se podle dostupných zdrojů chystají na konec roku 2023; APU pak na začátek roku 2024. Pravděpodobně budou fungovat jako konkurence architektur Intel Meteor Lake a jeho nástupce.