Apple plánuje využívat TSMC SoIC, spojování křemíku pokročilejší než CoWoS

Zatímco stávající polovodičovou výrobu nejdražších produktů limitují zejména kapacity pouzdření technologií CoWoS (Chip on Wafer on Substrate), průmysl pozvolna nasazuje technologii, která je v mnoha směrech pokročilejší: SoIC (System on Integrated Circuit). SoIC však není plnou náhradou CoWoS, spíše pro část situací, které lze řešit pomocí CoWoS, nabízí výhodnější řešení.

Na technologii CoWoS lze nahlížet ze dvou hledisek, které spolu souvisí. Jednak jako na spojování křemíku pomocí pájení (zjednodušeně řečeno zmenšené BGA, takže spoj mezi dvěma na sobě ležícími kousky křemíku tvoří kuličky z pájky) a jednak na něj lze nahlížet jako na proces spojování, který se děje na úrovni pouzdřících linek / továren (tzv. back-end). SoIC naproti tomu ke spojení křemíku nepotřebuje pájku, oba povrchy křemíku jsou vybavené měděnými kontakty, které se přímo dotýkají (křemíky leží přímo na sobě bez jakékoli mezery) a realizace tohoto rozhraní je prováděna na úrovni samotných továren polovodičové výroby (tzv. front-end).

Metody spojování čipletů (TSMC)

Výhody pak plynou zejména z faktu, že SoIC (díky absenci kuliček pájky) umožňuje vytvářet i řádově hustší (míněn počet kontaktů na plochu) rozhraní než jiné dosavadní metody s kuličkami pájky. Čiplety tak spolu mohou komunikovat prostřednictvím podstatně širší sběrnice, díky čemuž lze dosáhnout podstatně vyšší přenosové rychlosti, ale třeba i vyšší energetické efektivity (širší rozhraní na nižší frekvenci může být energeticky efektivnější, viz např. HBM namísto DRAM) nebo menších čipů.

Apple, který na svých produktech dosud využíval maximálně CoWoS, se v současnosti připravuje na nasazení SoIC v letech 2025-2026. V tomto technologickém závodu bude patrně předběhnut Nvidií, která rovněž na aktuálně dostupném hardwaru používá nanejvýš CoWoS, ale v letech 2024-2025 se očekává využití SoIC.

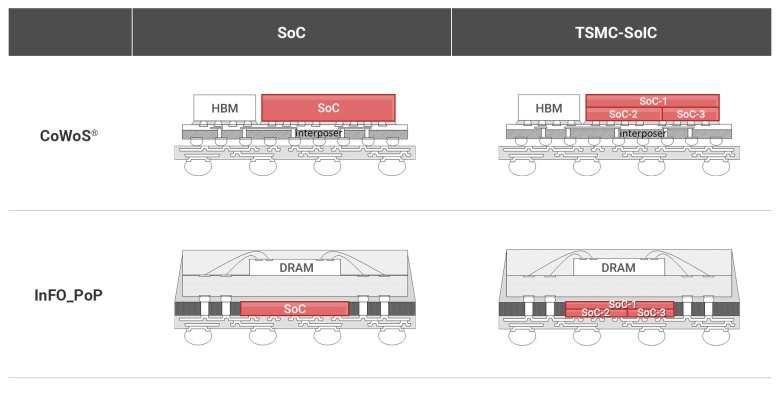

Příklady použití SoIC v kombinaci s CoWoS nebo InFO (TSMC)

Průkopníkem v nasazení SoIC byla AMD, která pomocí této technologie připojila V-cache k procesorovému čipletu (generace Zen 3). Technologii, byť ne ke spojení čip(let)ů, ale waferů, využila také Sony pro své obrazové snímače. AMD v současnosti využívá i kombinace CoWoS a SoIC, kdy na akcelerátorech řady Instinct MI300 spojuje funkční čiplety s HBM pomocí CoWoS a samotné vrstvené čiplety mezi sebou pomocí SoIC.