Drahý 3nm proces? Podle dostupných čísel by byl naopak ekonomickou výhrou

Redakce webu DigiTimes, která má obvykle informace o nových výrobních procesech z první (nebo jí blízké) ruky, publikovala článek, ve kterém v podstatě vysvětluje vysokou cenu příští generace iPhonů drahým 3nm procesem TSMC. Jenže když vezmeme v potaz čísla, kterými svá tvrzení dokládá, přestává vysvětlení dávat smysl.

Je známo (a není na tom co zpochybňovat), že každá další generace výrobních procesů je při ceně za wafer dražší než předchozí. Cena u posledních generací roste spíše o vyšší desítky procent oproti zaváděcí ceně předchozího procesu, řekněme o 50-60 % (dříve to bylo méně). Stejně tak je pravdou, že každá nová generace výrobního procesu zmenšuje tranzistory méně než ta předchozí. Mezigenerační nárůst počtu čipů na wafer je tak s každou generací menší, takže je vyšší cena kompenzována vyšším počtem čipů stále menší a menší měrou. Jenže…

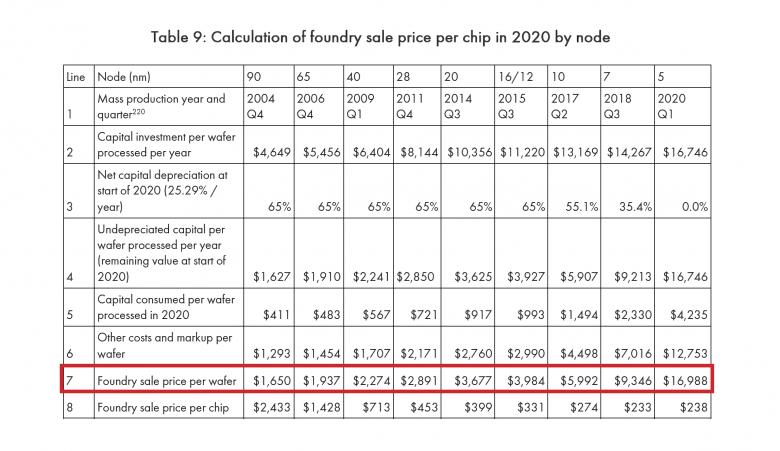

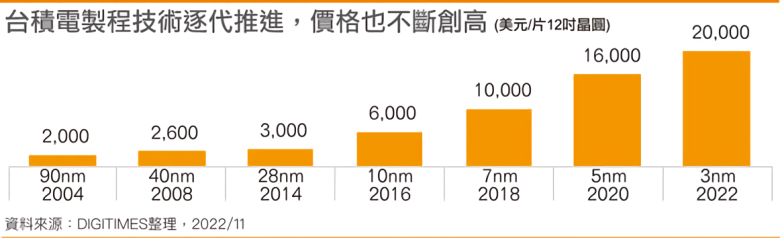

DigiTimes přišla s výše uvedeným grafem, kterým se snaží dokázat, že použití 3nm procesu TSMC na výrobu čipu Apple A17 výrazně zvýší náklady na čip a nakonec možná i cenu celého iPhonu. Předpokládejme, že čísla má DigiTimes správná a že 3nm wafer vyjde skutečně jen na 20 tisíc dolarů. Původní zprávy hovořily o ceně „výrazně přes 20 tisíc“, nicméně proces má určité zpoždění, Samsung má jistou (byť ne asi úplně plnohodnotnou) alternativu, poptávka klesá, takže TSMC může být motivovaná více tlačit na cenu a nabízet 3nm wafer jen za mizerných dvacet tisíc.

Jenže pak nevychází matematika. Cena by tedy oproti 5nm procesu ($16 000) vzrostla o 25 %, ovšem standardní 3nm proces umožňuje dosahovat až o 42 % nižší plochy na tranzistor, což znamená o 70 % vyšší denzitu, tedy až o 70 % více čipů na wafer (v praxi více, protože menší čipy přinášejí i efektivnější využití okrajových částí waferu). O 70 % více čipů při ceně waferu o 25 % (obé oproti 5nm výrobě) tak vede k poměrně značnému snížení výrobních nákladů, nikoli ke zvýšení.

Je však pravdou, že Apple má použít proces TSMC N3E, nikoli základní N3, přičemž N3E nedosahuje tak vysoké denzity (má jiné výhody). TSMC jistě nebude využívat čistě (nebo vůbec) variantu N3E 3-2 Fin určenou pro čipy orientované na výkon jako x86 procesory a GPU. Ta by se mohla objevit nanejvýš lokálně u velkých ARM jader, přičemž zbytek SoC vznikne na „zlaté střední cestě“ N3E 2-2 Fin nebo pro denzitu a nízkou spotřebu optimalizované N3E 2-1 Fin. Tyto dva procesy zvyšují mezigeneračně denzitu o 39 a 56 %. I kdyby denzita (~počet čipů na wafer) stoupla v průměru jen o 40 %, stále je to podstatně vyšší číslo než 25% zvýšení ceny na wafer.

Zkrátka a dobře, pokud je cena kolem $20 000 za wafer pravdivá a přitom má u 3nm generace produktů Applu dojít k nějakému zásadnímu zdražení, nelze toto zdražení zdůvodnit samotným procesem. Spíše by muselo jít o navýšení rozpočtu tranzistorů vysoko nad úroveň, kterou zvládá nový proces cenově vykompenzovat. Pak by samozřejmě zdražení nešlo na vrub 3nm procesu (neboť na 4nm nebo 5nm by takový čip byl ještě podstatně dražší), ale v důsledku strategického rozhodnutí Applu.