Lisa Su ukázala první 2nm Zen 6 wafer z TSMC

Původně se předpokládalo, že AMD bude 2nm proces ve vztahu k architektuře Zen 6 používat pouze k výrobě 32jádrových CCD určených pro serverový Zen 6-dense, jehož vydání se očekávalo v roce 2027. Pro klasickou serverovou řadu a PC segment se předpokládalo použití 3nm procesu (a vydání v roce 2026). MLID a RedGamingTech však nastínili, že i čiplety pro základní produkty s architekturou Zen 6 (tedy ty chystané na rok 2026) vzniknou na 2nm procesu.

Zen roadmapa (AMD)

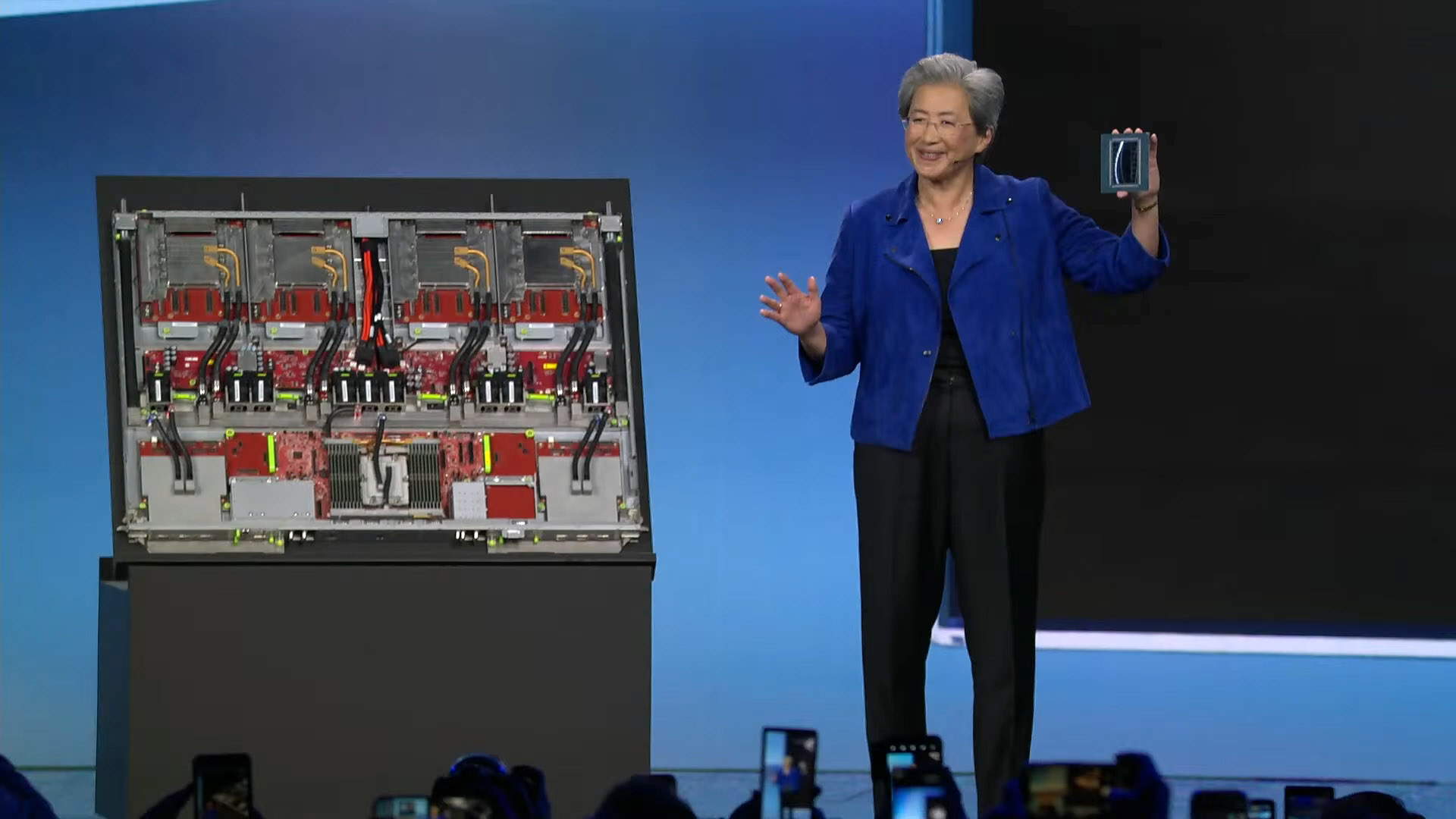

Nyní Lisa Su ukázala a AMD v tiskové zprávě potvrdila, že Zen 6 čiplety, které budou osazené na Epyc Venice, vzniknou na 2nm procesu TSMC a Epyc Venice bude vydaný v roce 2026. Tím je oficiálně potvrzeno, že AMD nasadí 2nm proces výrazně dříve, než se očekávalo.

- Desktopový Zen 6 může využít N2X proces a překonat 6 GHz

- Zen 6 APU počítají s 2nm i 3nm procesem, portfolio je masivní

Důvodem tohoto rozhodnutí (které s ohledem na plánování muselo padnout již docela dávno) je patrně plán Intelu nasadit s generací Nova Lake (2026) 2nm proces TSMC a již o rok později (2027) přejít na vlastní proces Intel 14A. Zda k tomu skutečně dojde, je samozřejmě otázkou, ale pro AMD je patrně podstatné se v rámci možností připravit na variantu, že ano.

V současnosti se očekává, že AMD bude využívat 2nm proces na 12- a 32jádrové Zen 6 čiplety, zatímco pro monolitické konfigurace využije 3nm proces. Ten by se měl objevit i na centrálních čipletech mobilních procesorů, zatímco u desktopových může být využita levnější 6nm technologie.

AMD zároveň oznámila, že úspěšně validovala Epyc 5. generace (tj. stávající Zen 5 / Turin) vyrobený z křemíku v továrně TSMC v Texasu (USA).