TSMC, half-nodes a 40nm fiasko

Kapitoly článků

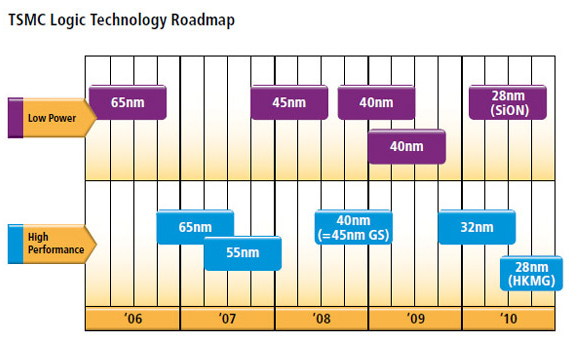

Vraťme se k TSMC, kterou jsme naťukli už v úvodu. Asi jste zaznamenali, že TSMC (ale i řada dalších výrobců) nabízí většinu procesů v různých verzích, které se liší především cenou, spotřebou, dosažitelnou frekvencí a denzitou. To platí i pro TSMC. Dlouhá léta držela tradici rychlého (a dražšího) SOI procesu, kterým se vyráběly hlavně procesory, a pak levnější (a asi o 10-15% pomalejší) bulk proces vhodný pro grafické čipy (později pak přibyly ještě low-power „LP“ varianty, ale ty zatím nechme). Právě bulkový proces byl pro TSMC klíčový a díky jedné specialitě, kterou kdysi žádný jiný výrobce nenabízel, se TSMC stala hlavním producentem grafických čipů na světě.

Chang Morris, CEO TSMC

Zmíněnou specialitou byly tzv. „half-nodes“, výrobní půlkroky. Zatímco ostatní výrobci uvedli 250nm proces a roky, po které se pachtili s přípravou 180nm a nemohli nabídnout nic jiného, TSMC „starý“ proces mírně vylepšila a uvedla jako 220nm. Tak to dělala po dlouhá léta, až k sobě stáhla všechny významnější zákazníky grafického průmyslu (ze kterých dnes zbyla Nvidia a - tehdy - ATI, dnes už součást AMD). Především half-nodes jako 150nm, 110nm, ale i 80 a 55nm byly velice úspěšné a obě strany na nich vydělaly nemalé peníze.

Když došlo na 45nm (bulk) proces, zaznamenala TSMC problémy s jeho přípravami a s oficiálním odůvodněním „rozdíl mezi 45 a 40nm je tak malý, že 45nm přeskočíme“ došlo pouze na přejmenování a problémy se řešily dál. Tak se ze 45nm bulk stal 40nm bulk. Protože takový přístup není právě košer, měl výrobce přichystaný jeden jakýs-takýs argument: 40nm bulk proces (ve skutečnosti 45nm bulk) dosahuje vyšší denzity, než 45nm low-power proces, a proto si lepší označení zaslouží. Takový argument ve srovnání s konkurencí příliš neobstojí, denzita 45nm procesu TSMC je nižší než u většiny konkurentů a s přihlédnutím ke grafům Davida Kantera je možné, že například 45nm SOI proces od IBM je na tom lépe, než „40nm“ bulk od TSMC.

Kromě přejmenování způsobila TSMC zmatek i v zažitém značení, protože to, co bylo z hlediska ostatních výrobců vnímáno jako half-node (půlkrok) byl pro TSMC full-node (hlavní výrobní proces). Situaci to komplikuje hlavně kvůli tomu, že se obojí liší vlastnostmi a použitelností. Half-nodes byly typicky levnější, ale dosahovaly nižších frekvencí a nepodporovaly nejnovější technologie (např. rozdíl v implementaci low-K dielektrika u 130/110 nm), kdežto full-nodes byly dražší, rychlejší a výrobci je obvykle využívali pro klíčové produkty.

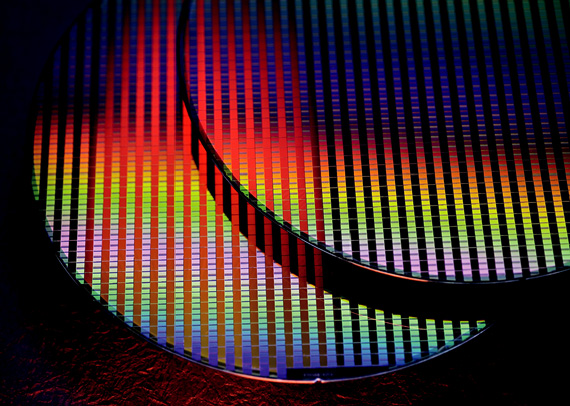

Taková změna výrazně nabourala roadmapy obou výrobců grafických čipů, následky jsou patrné dodnes. Vyplývá to nejen z projektování čipů pro určitý cílený rozměr (a tím i cenu), ale také absenci toho, co známe pod názvem „die-shrink“. Die-shrink (ve správném významu) znamená přechod čipu za full-node na half-node. Většinu funkčních bloků čipu stačilo jen opticky zmenšit bez potřeby celkového přepracování (které je jinak třeba) a výrobci, kteří byli na tento postup po léta zvyklí, s ním počítali ve svých strategiích (například navrhli rozměry grafického čipu tak, aby jeho die-shrink, který plánovali uvést na trh později, měl ještě dostatečné rozměry pro zachování plné šířky sběrnice a mohl na trhu svého předchůdce efektivně nahradit).

Byť se důvody TSMC od důvodů Intelu liší (což je dáno odlišným obchodním modelem obou výrobců), je výsledek v podstatě stejný a neradostný. Ostatním výrobcům nezbyde než přijít s více či méně podobnou strategií. A tak je možná jen otázkou času, kdy při výběru procesoru budeme muset mít na paměti, že ten nový 10 nanometrový vlastně není o nic lepší než starý 12 nanometrový, protože tentokrát výrobce nevyvíjel, ale přejmenovával.