TSMC rozjíždí sériovou výrobu prvních „3D“ čipů

Xilinx se rozhodl využít nové 3D (CoWoS) technologie v rámci 28nm výroby pro komunikační čip Virtex-7 HT (FPGA), který je určený pro rychlé optické sítě. Čip integruje mj. šestnáct 28Gbps a sedmdesát dva 13,1Gbps transceivery.

Podle vyjádření obou firem jde o vůbec první heterogenní řešení tohoto typu, které půjde na trh. Krom Virtex-7 HT ale už nějaký ten pátek běží i výroba čipů řady Virtex-7 2000T a Virtex-7 X1140T, což jsou homogenní řešení vyráběná 3D (CoWoS) technologií.

Krom 28nm generace pracuje Xilinx na SoC firemní Ultrascale architektury, která jsou určená pro 20nm CoWoS a 16nm FinFET CoWoS proces.

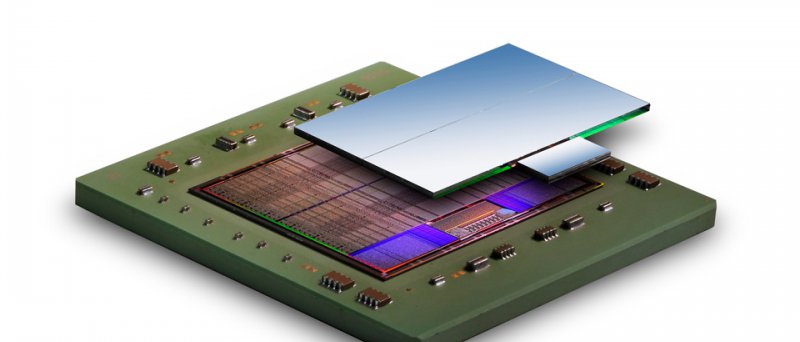

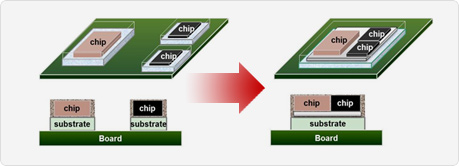

Technologie TSMC CoWoS umožňuje výrobu tzv. 3D integrovaných obvodů prostřednictvím TSV - Through Silicon Via(s), spojů procházejících skrz křemík, což umožňuje integrovat více čipů do jednoho zařízení. Výhodou je možnost snazší implementace širokých sběrnic a vysokého množství datových cest při menších výsledných rozměrech a nižších energetických nárocích oproti standardním (planárním) procesům. Touto cestou lze optimalizovat i výrobní náklady - například tím způsobem, že kritické části čipu budou vyráběné modernějším procesem, zatímco méně důležité obvody zůstanou na starší (výrazně levnější) verzi.