Vrstvení necílí jen na výkon. Díky LoDTC může generačně snížit spotřebu

Vrstvení pomalu ale jistě prošlo přerodem, kdy se z papírové technologie stává proces využívaný komerčním hardwarem. Loni si jej Intel vyzkoušel na mobilním SoC/SiP Lakefield, letos se ho dočkáme od AMD v podobě implementace tzv. V-cache na Zen 3. I když by stále z pohledu zákazníka mohlo jít o technologii (respektive soubor technologií), na kterém nestojí klíčové dostupné produkty a který může být přeřazen na druhou kolej, roadmapy výrobců čipů dost jasně ukazují něco jiného. Většina produktů budoucích generací nějakým způsobem tyto technologie využívá a čím vzdálenější plány, tím více jich je. Není divu. Intervaly ve vývoji nových křemíkových procesů se prodlužují, jejich přínos je generaci od generace nižší, a tak je potřeba hledat alternativy, které tyto nedostatky vykompenzují.

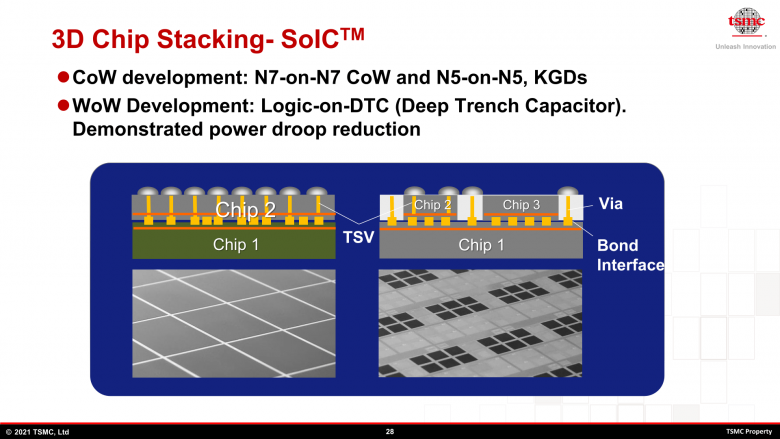

Až dosud se mluvilo hlavně o přístupech zvyšujících výkon, snižujících plochu, zvyšujících šířku sběrnic propojujících kousky křemíku a podobně. TSMC ale pracuje i na technologii, která má mít pozitivní vliv na energetické nároky. Vychází z tzv. WoW vrstvení, tedy Wafer on Wafer (wafer na waferu). Jmenuje se Logic-on-DTC, kde DTC znamená Deep Trench Capacitor (hluboce zanořený kondenzátor). Spodní vrstva tedy nese tyto kondenzátory (DTC) a na ní leží vrstva nesoucí klasickou logiku, která tyto kondenzátory využívá.

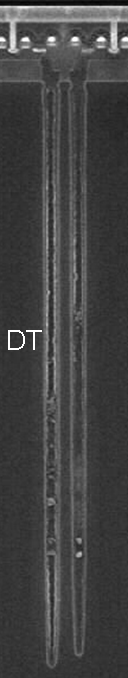

Samotné DTC nejsou ničím novým, v polovodičovém průmyslu už se nějakou dobu využívají. Umožňují totiž umístění kondenzátoru přímo do křemíku čipu, přičemž při minimálních nárocích na plochu (jsou výrazně vertikální) dosahují slušné kapacity. Další výhoda vyplývá z implementace přímo do křemíku, takže mohou být tak blízko cílenému obvodu, jak je to možné.

řez waferem s IBM DTC (WikiChip)

Dosud se využívaly jak v pamětech (IBM eDRAM, kterou přímo tvoří), tak i v logice, kde mohou být využívané jako lokální paměť / cache s velmi vysokou denzitou, jako oddělovací kondenzátory, filtry a podobně.

TSMC přichází s myšlenkou jejich využití při vrstvení, kdy by spodní vrstva (wafer) byla tvořena čistě těmito kondenzátory (DTC). Kompenzovala by energetické poklesy a tím umožnila snížení energetických nároků takového řešení, které zhruba odpovídá snížení energetických nároků jedné generace výrobního procesu (to je poněkud obecné tvrzení, ale můžeme si jej konkretizovat kontextem: 5nm proces oproti 7nm sníží energetické nároky o 30 %, 3nm proces oproti 5nm o 25-30 % - platí pro stejný návrh čipu a stejné taktovací frekvence).

V současné době je jediným veřejně známým zákazníkem TSMC, který se společností pracuje na implementaci do konkrétního produktu, společnost Apple. Ta je zaměřená na mobilní segment, ve kterém dává použití technologie snižující energetické nároky největší smysl. Je však možné, že s LoDTC v tichosti experimentují i další značky a časem se jejího využití dočkáme i v segmentu osobních počítačů.

TSMC, ilsutrace: WikiChip

Diskuse ke článku Vrstvení necílí jen na výkon. Díky LoDTC může generačně snížit spotřebu