Plány TSMC na 2027: 1,6nm proces a pouzdření s ≥12 HBM4

Na Semicon Taiwan 2024 vystoupil vice-prezident TSMC pro pouzdření, Jun He, s přednáškou „3D IC / CoWoS for AI Summit“, ve které předestřel výhled na 4-6 let vzdálenou budoucnost. Podle odhadů TSMC dosáhne polovodičový průmysl roku 2030 hodnoty bilionu dolarů a 40 % z tohoto trhu budou tvořit AI + HPC produkty.

Pro TSMC to znamená přizpůsobovat nabídku produktů a služeb tomuto rychle rostoucímu trhu. Vzhledem k tomu, že nejvýkonnější akcelerátory již nyní překonaly požadavky na plochu křemíku, kterou lze zpracovávat monoliticky, to znamená ještě větší zaměření na čiplety a podporu HBM pamětí.

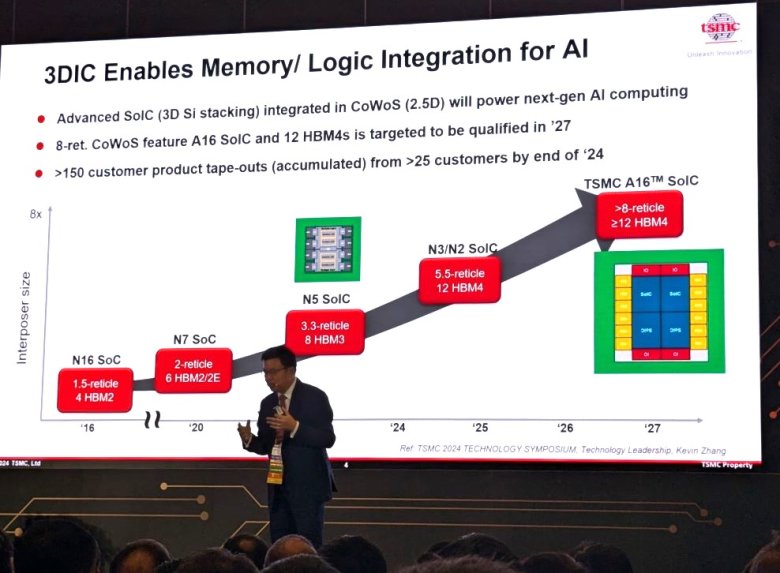

Výhled na rok 2027 (TSMC)

V kratším časovém horizontu, tedy pro rok 2027, si TSMC stanovila za cíl nabídnout proces A16 (=1,6nm, 16A) ve spojení s novou generací CoWoS pouzdření, která nabídne využitelnou plochu o minimálně osminásobku tzv. reticle limitu (=limit rozměrů pro největší monolitický čip, aktuálně kolem 800 mm², ale v budoucnu se může zmenšovat). Na takovou plochu by se mělo (krom samotných funkčních čipletů) vejít i minimálně 12 čipů HBM4. Připomeňme, že aktuální nejvýkonnější produkty jsou vybaveny 6-8 čipy HBM3 a probíhá přechod na HBM3E.

S očekávanou propustností 1,5-2 TB/s pro jeden čip (formálně jde o modul, ale pro srozumitelnost zůstaňme u „čipů“) to znamená 18-24 TB/s pro akcelerátor. Při kapacitě až 64 GB na čip by jeden takový akcelerátor mohl hypoteticky nabídnout až kapacitu 768 GB. V roce 2027 ale asi půjde o nižší hodnoty, papírového maxima technologie dosáhne nejspíš až koncem své éry. I polovina (384 GB) by ale byla vcelku impozantní.

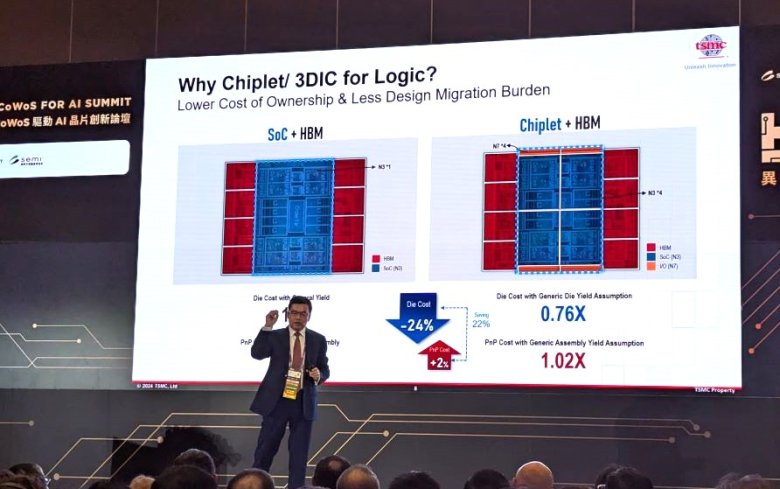

Finanční výhody použití čipletů (TSMC)

He dále zveřejnil odhad TSMC, o kolik výrobu zlevňuje použití čtyř čipletů namísto jednoho monolitu: Náklady na výrobu čipletů podle něj dosahují 76 % toho co náklady na výrobu monolitu, přičemž navýšení nákladů v důsledku složitějšího pouzdření (oproti ceně monolitu s HBM) činí jen 2 %.