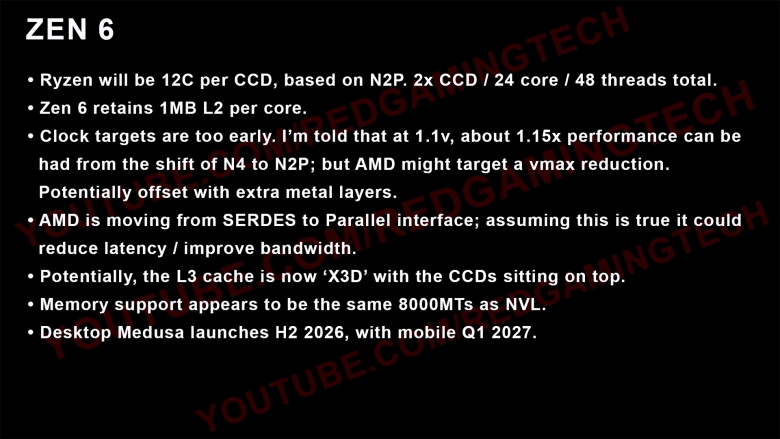

Zen 6: O 50 % více jader, >10 % IPC a +15 % taktů při stejném napětí

Celkový výkon (jádra, IPC, takty)

Současné desktopové a serverové procesory Zen 5 jsou postavené na osmijádrových čipletech. Delší dobu je známo, že Zen 6 v tomto ohledu přinese významnou změnu, protože počet jader na čiplet stoupne z osmi na dvanáct, tedy o 50 %. Druhou změnou bude nárůst IPC, který sice nebude nijak extrémní (přes 15 %), ale při 10-15 % bude v kombinaci s vyšším počtem jader se bude významně podílet na mezigeneračním posunu výkonu.

RedGamingTech dále přinesl informaci, podle kterém Zen 6 díky 2nm procesu TSMC umožňuje při stejném napětí posunout taktovací frekvenci o 15 % a zajistit tím další posun výkonu - podobný jaký přinese IPC.

Pokud budeme výkon čipletu Zen 5 považovat za 100 %, pak nárůst jader (×1,5), maximální nárůst IPC (×1,15) a maximální nárůst frekvence (×1,15) znamená potenciál až pro 1,98×, tedy prakticky 2× vyšší výkon. Pravděpodobnější však je, že nárůst IPC bude někde mezi 10-15 %, řekněme kolem 12 % a část z nárůstu taktů AMD obětuje na snížení napětí a tím snížení spotřeby, což bude s ohledem na vyšší počet jader nejspíš nutné. Realističtější je tedy očekávat maximálně 1,5 (jádra) ×1,12 (IPC) ×1,1 (takty) zhruba 1,85× vyšší výkon v dobře škálující vícejádrové zátěži.

2nm výrobní proces

Když TSMC na přelomu dubna a května zveřejnila nové roadmapy, vyjádřili jsme pochybnosti nad možností nasazení procesu N2X s první vlnou produktů Zen 6. Tento náhled nyní RedGamingTech potvrzuje: Čiplety Zen 6 budou nakonec vyráběné procesem N2P, tedy druhou (nikoli třetí) verzí 2nm procesu TSMC. Pokud se N2X v portfoliu AMD objeví, bude to buďto někdy později za éry Zen 6 (například jako refresh) nebo až se Zen 7. Proces N2X se liší potenciálně vyššími maximálními takty, jde však o rozdíl nižších jednotek procent.

Nejasný je zatím způsob implementace L3 cache. Není totiž jisté, zda AMD implementuje základní (48MB) L3 cache jako součást 2nm křemíku (podobně jako tomu bylo u dosavadních procesorů), nebo ji přesune už v základní podobě na úroveň V-cache, tedy v podobě 6-4nm vrstvičky křemíku umístěné zespodu čipletů. S tím, že „X3D“ řada by místo 48MB varianty nesla třeba 96MB variantu. O podobném konceptu se mluvilo už dříve, ale dosud není jasné, kdy (či zda) AMD tuto změnu nasadí.

Paměťový řadič by měl podporovat až 8000 MT/s (patrně pro DDR5) a nic se zatím nemění na očekávaném datu vydání kolem podzimu 2026 pro desktop a v prvním kvartálu 2027 pro mobilní produkty.