Zen 6 vznikne na N3E + N4C, Zen 6 Halo-APU i Playstation 6 čeká 3D pouzdření

Zen 6 je poměrně vzdálená generace. Zatímco podle původních plánů neměla být prodleva po Zen 5 příliš dlouhá, nakonec AMD nestihla s pátou generací dotáhnout všechny změny, které chtěla, a tak jich u Zen 6 bude muset být víc. Mluvilo se například o upraveném schedulingu nebo novém paměťovém rozhraní nad rámec původně chystaných změn. Zatímco měl Zen 6 stát především na zvýšeném počtu jader a novém procesu, nakonec bude změn víc a některé asi budou mít i trochu pozitivní dopad na IPC. Situace dost připomíná Zen vs. Zen 2, kdy původní Zen měl být po architektonické stránce podobnější finálnímu Zen 2, ale z časových důvodů nestihla AMD implementovat vše a tak Zen 2, který měl být původně jen převodem půvoního návrhu x86 jádra na nový výrobní proces vylepšený navýšením počtu jader, přišel jako nová architektura s vyšším IPC.

Procesorová roadmapa (AMD)

O Zen 6 dále víme, že základem čipletové verze bude křemík s 12 jádry Zen 6 (zatím to vypadá, že všechny budou bez „c“). Nativní tedy budou 12- a 24jádrová konfigurace, ostatní vzniknou na bázi částečně deaktivovaného křemíku. Tyto čiplety najdou uplatnění i v segmentu APU, takže i standardní řada APU vznikne na bázi 12jádrového křemíku.

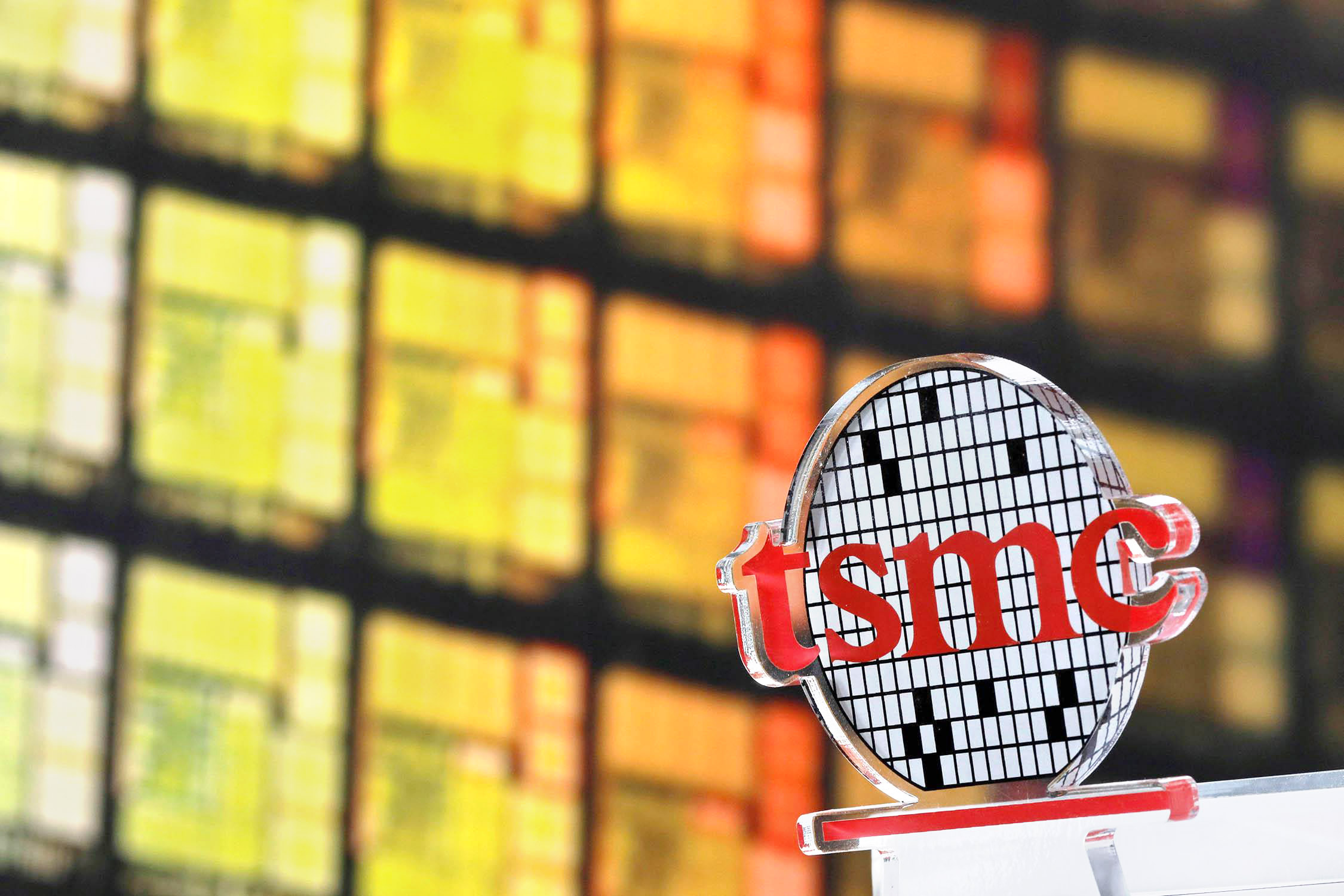

Podle aktuálních zpráv od leakera Zhangzhongzhao rozhodla AMD o použití procesu TSMC N3E pro procesorové čiplety (CCD) a TSMC N4C pro centrální čiplety (IOD). Proces N3E je čtvrtou verzí 3nm procesu TSMC:

- N3(B)

- N3P

- N3E

N3B známe z Intel Arrow Lake, o rychlejší N3P se mluvilo v souvislosti s Intel Lunar Lake (ba co mluvilo, tato informace byla i v jednom ze slajdů Intelu), ale nakonec se Intel i v tomto případě rozhodl pro základní N3B. Novinkou N3E je konfigurovatelnost procesu i v rámci jednoho čipu. Pro části čipu, kde je klíčový výkon, může být použita rychlá varianta (N3E 3-2 Fin), která sice oproti 5nm procesu snižuje plochu jen o 15 %, ale výkon (takty) zvyšuje až o 33 %. A naopak tam, kde nejde o výkon (řadiče, rozhraní ap.) je možné použít úspornou variantu (N3E 2-1 Fin), která snižuje plochu o 36 %, ale výkonu přináší maximálně 11 % navíc. Pokud zůstane frekvence na úrovni 5nm produktu, pak ale oproti němu ušetří 30 % energie.

| TSMC | |||

|---|---|---|---|

| proces | denzita | výkon | spotřeba |

| 7nm (N7) | +59 % vs. N10 | +35-40 % vs. N10 | -40 % vs. N10 |

| 7nm (N7P) | ? | +7 % vs. N7 | -10 % vs. N7 |

| 7nm+ (EUV / N7+) | +20 % vs. N7 | +10 % vs. N7 | -15 % vs. N7 |

| 6nm (N6) | +18 % vs. N7 | ? | ? |

| 5nm (N5) | +80 % vs. N7 | +15 % vs. N7 | -30 % vs. N7 |

| 5nm (N5P) | ? | +7 5 % vs. N5 | -10 % vs. N5 |

| 4nm (N4) | +6 % vs. N5 | téměř beze změny | beze změny |

| 4nm (N4P) | +6 % vs. N5 | +11 % vs. N5 +6 % vs. N4 | -22 % vs. N5 |

| 4nm (N4X) | ? | +15 % vs. N5 @1,2V +4 % vs. N4P @1,2V | ? |

| 4nm (N4C) | +8 % (?) | - (?) | - (?) |

| 3nm (N3) | +70 % vs. N5 2,9× vs. N7 | +10-15 % vs. N5 +32 % vs. N7 | -25-30 % vs. N5 |

| 3nm (N3B) | +60 % vs. N5 | +10-15 % vs. N5 +32 % vs. N7 | -35 % vs. N5 -43 % vs. N7(?) |

| 3nm (N3P) | +4 % vs. N3E | +10 % vs. N3E | -5-10% vs. N3E |

| 3nm (N3E 3-2 Fin) 3nm (N3E 2-2 Fin) 3nm (N3E 2-1 Fin) | +18 % vs. N5 +39 % vs. N5 +56 % vs. N5 | +33 % vs. N5 +23 % vs. N5 +11 % vs. N5 | -12 % vs. N5 -22 % vs. N5 -30 % vs. N5 |

| 3nm (N3S) | ? | ? | ? |

| 3nm (N3X) | +4 % vs. N3P | +15 % vs. N3P | ? |

| 3nm (N3A) | ? | ? | ? |

| 2nm (N2) | +10% vs. N3 +>15% vs. N3E | +13 % vs. N3E 2-1 +10-15 % vs. N3E | -33 % vs. N3E 2-1 -25-30 % vs. N3E |

| 2nm (N2P) | +9-13 % vs. N2 | +10-12 % vs. N2 | ? |

| 2nm (N2X) | ? | ? | ? |

| 1,6nm (A16) | +7-10 % vs. N2P +17-24 % vs. N2 | +6-10 % vs. N2P +17-23 % vs. N2 | -15-20 % vs. N2P |

Centrální čiplet využije N4C proces, což je 4nm proces, který je optimalizovaný pro denzitu a výrobní náklady, takže čip na něm vyrobený stojí o 8,5 % méně než na stávající 4nm výrobě. Přinejmenším část úspory TSMC dokázala nahnat na SRAM, kterou se standardními 5nm a 4nm z časových důvodů příliš neoptimalizovala.

V době generace Zen 6 najde širší uplatnění i 3D pouzdření, které se krom APU rozšíří i do segmentu konzolí. Podle zmíněného leakera už u Sony padlo rozhodnutí, že SoC/APU pro Playstation 6 využije 3D pouzdření. Microsoft s příští generací Xboxu zatím váhá. Pokud alespoň Sony někdy v letech 2026-2027 počítá s 3D pouzdřením, pak lze předpokládat, že tato metoda bude již natolik široce i cenově dostupná, že ani pro desktopové procesory nebude představovat významná navýšení nákladů (alespoň ne tedy nad rámec výkonnostního přínosu). Zatím však není jasné, jakou konkrétní metodu AMD a Sony použije (CoWoS, InFO, SoIC…).

Závěrem připomeňme, že pokud vše půjde zcela hladce, bude čipletová verze (desktop) Zen 6 k vydání připravena na konec roku 2026 a mobilní APU na CES 2027.

Chiphell via WCCFTech