Nové procesy zastavily škálování SRAM, 3nm mu už nepřináší nic

Intervaly mezi nástupem nových generací procesorů se prodlužují, výkonnostní nárůst (frekvence) je s každou další generací nižší, snížení plochy rovněž a snížení spotřeby také. Právě snižování plochy (zhruba na polovinu) bylo základním pohonem vývoje hardwaru: S každou další generací bylo možné do čipu integrovat 2× více tranzistorů a tím zvýšit výkon a/nebo rozšířit výbavu čipu, aniž by se to výrazněji promítlo do výrobních (a tudíž i prodejních) nákladů.

Zatímco se v kontextu celkové denzity (počtu tranzistorů na jednotku plochy) nebo denzity logických obvodů obvykle mluví o zpomalování mezigeneračního posunu, denzita paměti SRAM, na které stojí prakticky všechny cache a registry současných čipů, se zastavila prakticky úplně.

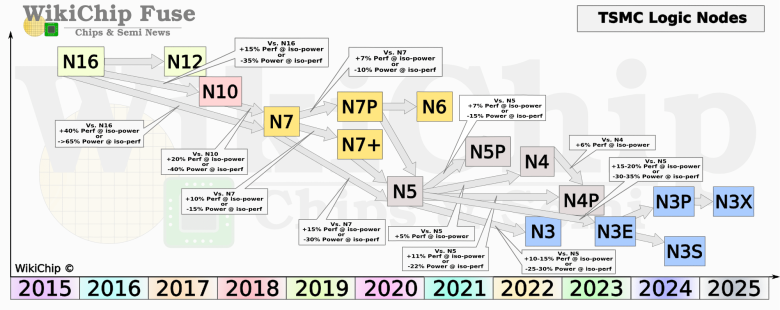

Jak je patrné z grafu WikiChip, poslední citelnější posun v tomto směru přinesl 7nm proces. U 5nm je již snížení plochy podstatně slabší a 3nm procesy nepřinášejí v podstatě nic. Jenže jednotka plochy 5nm procesu stála zprvu o ~80 % víc než jednotka plochy 7nm procesu. U 3nm procesu oproti 5nm je nárůst ceny za jednotku plochy křemíku zhruba 50%. Takže čip(let) tvořený čistě SRAM by nejenže na 3nm procesu nebyl levnější než na 5nm, ale tatáž kapacit aby vyšla o 50 % dráž.

Výrobci čipů se tomu samozřejmě (technologicky) brání, ale jedna věc je kompenzovat klesající mezigenerační přínosy a druhá (zcela odlišná věc) je potýkat se mezigeneračním zdražení, které není vyváženo ani minimálním přínosem.

AMD i Intel se k situaci staví velmi podobně (byť Intel dospěl k obdobným závěrům s letitým zpožděním oproti AMD). Jde o rozdělení čipů na více kusů křemíku (ať už jde o jejich skládání vedle sebe - čiplety / dlaždice - nebo na sebe - vrstvy). Cache je v rámci možností oddělena od výpočetních jader (vyráběných novějšími procesy) a umístěna do křemíku vyráběného starším procesem.

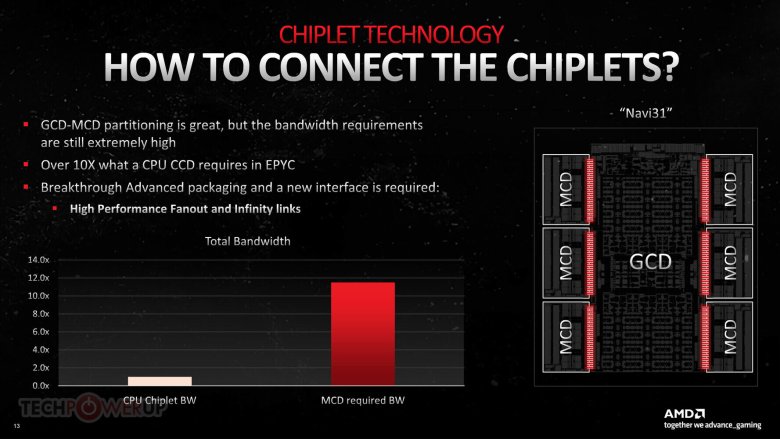

Jedním příkladem mohou být čiplety grafické architektury AMD RDNA 3, kde je cache (SRAM) umístěna v samostatných 6nm čipletech kolem 5nm jádra. Nebo výpočetní GPU Intel Ponte Vecchio, kde je rovněž caches (SRAM) oddělena z 5nm výpočetních dlaždic (modře) a umístěna na dlaždice vyráběné procesem Intel 7 (10nm ESF, šedočerně):

Druhý typ řešení využívá AMD a označuje ho jako V-cache, kdy je SRAM v podobě tenkého 6nm plátku křemíku navrstvena na (například) 5nm čiplet s procesorovými jádry (Ryzen 7000X3D nebo serverové procesory Epyc Genoa-X, které se brzy objeví na trhu).

Třetí typ řešení se využívá tam, kde jednotlivé čiplety nejsou spojeny prostě přes pouzdro nebo pomocí malých můstků, ale přes křemíkovou základnu (interposer), na které jsou umístěné. Tato základna nabízí velkou plochu, takže se naskýtá otázka: Proč ji nevyužít také pro SRAM?

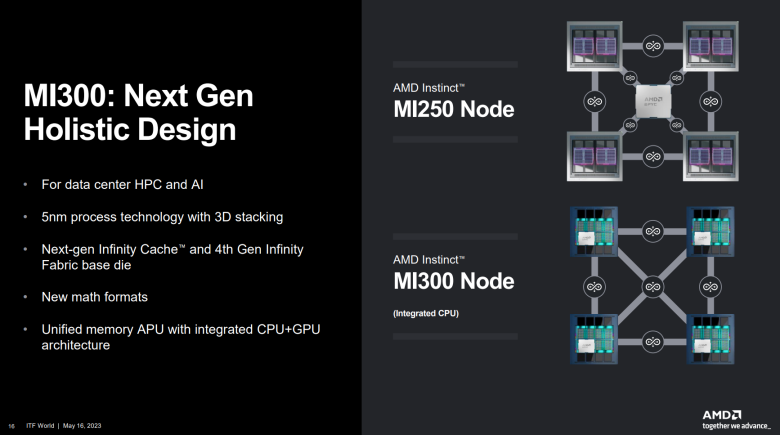

Proslýchá se, že takové řešení by mohl využívat mobilní procesor Meteor Lake od Intelu a potvrzeno je to u CDNA 3 / Instinct MI300 od AMD (obojí se má objevit do konce letošního roku):

- Tajnou zbraní Intel Meteor Lake má být až 512MB Adamantine Cache

- AMD představila MI300 pro El Capitan: 24× Zen 4 + CDNA 3 + Infinity Cache + HBM3

Problém je, že jde ve všech případech o kroky, které jsou jednorázovou kompenzací. Zatímco nové výrobní procesory, které ještě SRAM zhušťovaly, přinášely prostor pro posun s každou generací, přesun SRAM do samostatného kousku křemíku na cenově výhodnější proces se odehraje jednou a tím je výhoda vyčerpána. S každou další generací produktů už bude potřeba pro narůstající cache zvětšovat i plochu křemíku a tím pádem i cenu produktu.

Jistě, ještě 5nm půjde u dražších produktů (nebo u levnějších - až časem klesne jeho cena) využít jako proces zvyšující denzitu SRAM, ale pak už (4nm, 3nm) procesy nepřinášejí v tomto ohledu nic (krom zmíněné vyšší ceny). Z tohoto pohledu zbývá určitý prostor u produktů, které si s ohledem na vyšší prodejní cenu mohou dovolit křemíkovou podložku (interposer), kde bude na určitou dobu pro SRAM prostoru dost.

Alternativně je tu ještě kombinace čipletů a vrstvení, kterou trochu naťukla architektura RDNA 3, ale která se z pochopitelných důvodů zatím nedostala do fáze sériové výroby. Připomeňme, že GPU Navi 31 / 32 přesouvá paměťový řadič a SRAM do čipletů (MCD) umístěných kolem centrálního čipletu s funkčními jednotkami (GCD) a nadto umožňuje na tyto paměťové čiplety (MCD) navrstvit další SRAM, pokud by kapacita integrované nestačila (vzhledem k omezením výkonu RDNA 3 však kapacita SRAM více než stačí, takže na vrstvení nedošlo). Tento způsob ale může najít uplatnění v budoucnu, kdy pro samotné navyšování plochy SRAM čipletů již nebude prostor.